Zero-layer alignment mark structure for photo-etched pattern on medium substrate

A zero-layer alignment mark, medium substrate technology, which is applied in the photoengraving process, optics, instruments and other directions of the pattern surface, can solve the problems of inconvenient alignment, non-special position, easy confusion, etc., and achieves easy searching. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

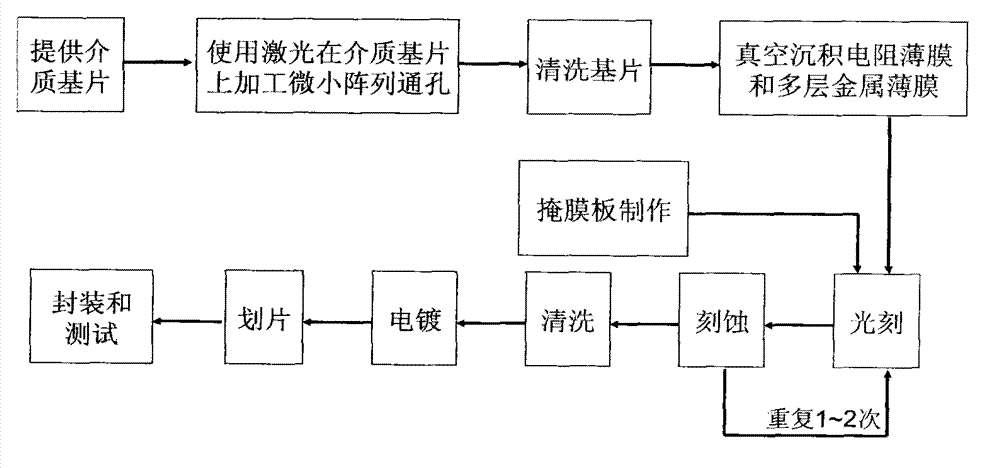

Method used

Image

Examples

Embodiment 1

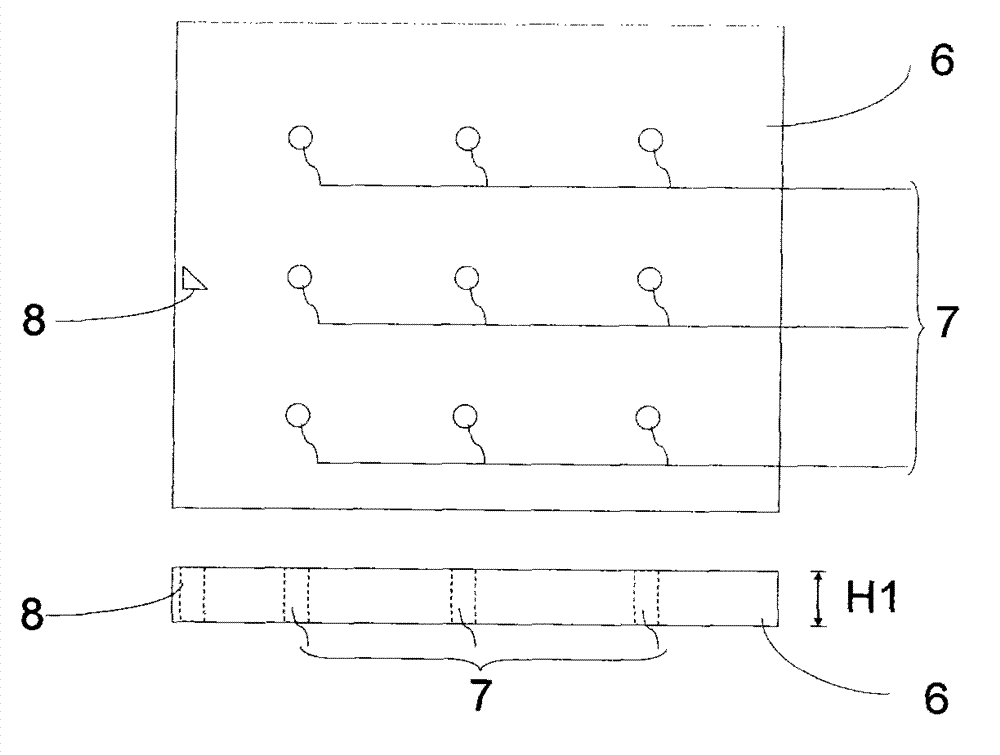

[0030] see figure 2 , the zero-layer alignment mark structure 8 is a longitudinal through hole arranged at the edge of the dielectric substrate 6 and it is a right triangle. In this embodiment, the dielectric substrate 6 where the zero-layer alignment mark structure 8 is located is made of alumina ceramics with a purity of more than 99.6%, the plane size is 50.8mm x 50.8mm, and the thickness H1 is 0.635mm.

Embodiment 2

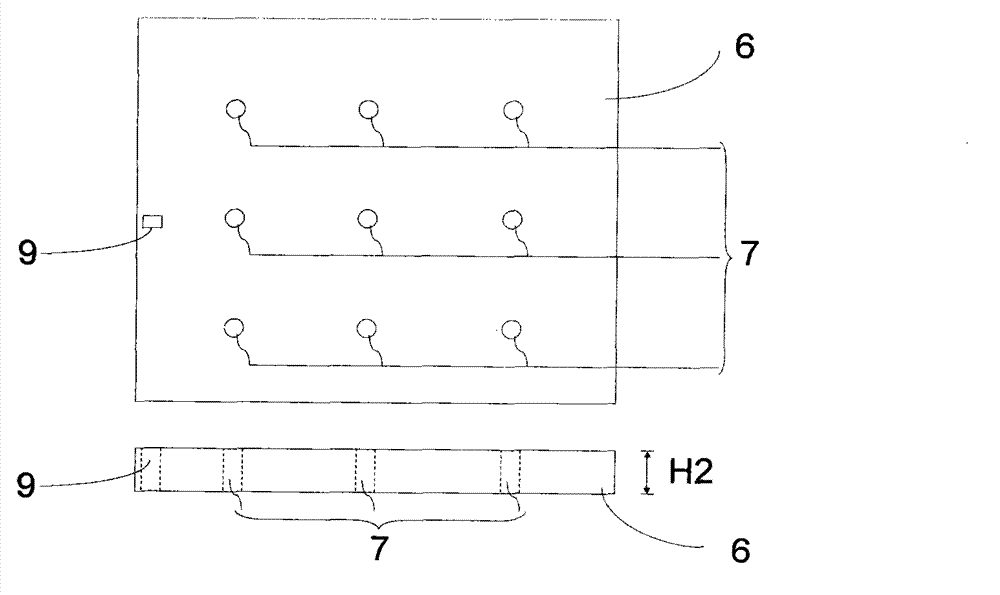

[0032] see image 3 , the zero-layer alignment mark structure 9 is a longitudinal through hole disposed at the edge of the dielectric substrate 6 and is a rectangle. In this embodiment, the dielectric substrate 6 where the zero-layer alignment mark structure 9 is located is made of alumina ceramics with a purity of more than 99.6%, the plane size is 50.8mm×50.8mm, and the thickness H2 is 0.254mm.

Embodiment 3

[0034] see Figure 4 , the zero-layer alignment mark structure 10 is a longitudinal through hole disposed on the edge of the dielectric substrate 6 and is a right-angled trapezoid. In this embodiment, the dielectric substrate 6 where the zero-layer alignment mark structure 10 is located is made of sapphire, has a plane size of 50.8 mm×50.8 mm, and a thickness H3 of 0.508 mm.

[0035] In the fabrication process of microwave thin film hybrid integrated circuit, use Figure 2 to Figure 4 The zero-layer alignment mark structures 8, 9, 10 described in can ensure that the microwave thin film hybrid integrated circuit on the dielectric substrate is manufactured at its preset position.

[0036] In summary, a zero-layer alignment mark structure for photolithographic patterns on a dielectric substrate according to the present invention is a right-angled longitudinal through hole arranged at the edge of the dielectric substrate, which can ensure that the micro-array metallization The a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More