Method for manufacturing mask read-only memory

A manufacturing method and mask read-only technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of transistor work function and feature size that cannot form resistance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

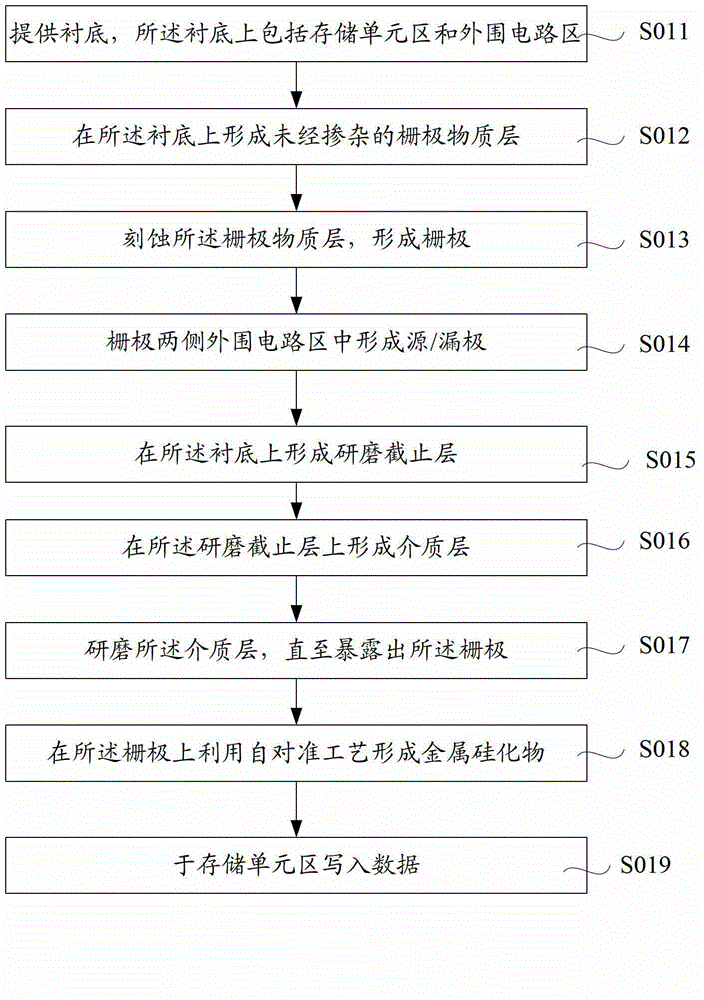

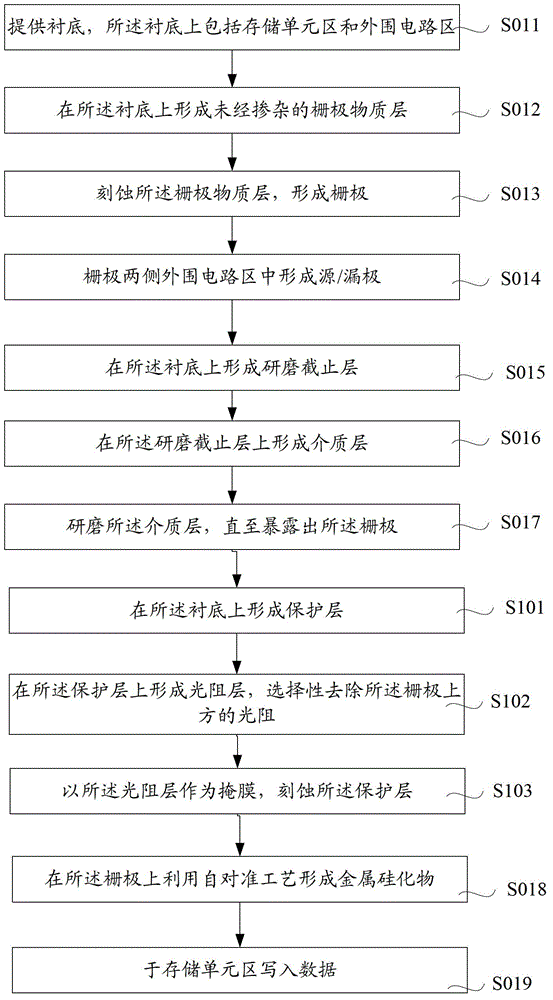

[0039] As mentioned in the background art, the existing manufacturing method of the mask ROM has the problem of incompatibility with the logic process. Therefore, the present invention provides a method for manufacturing a masked read-only memory, using an undoped gate material layer to form a gate, and forming a metal silicide on the gate. Such a process has a good relationship with logic processes. The compatibility solves the problem that the use of doped polysilicon and tungsten silicide gates affects the work function and feature size of transistors and the problems that devices such as resistors cannot be formed.

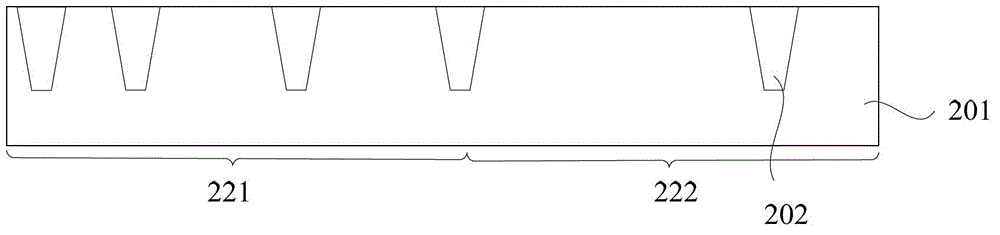

[0040] The present invention will be described in more detail below with reference to the accompanying drawings, wherein preferred embodiments of the present invention are shown, it should be understood that those skilled in the art can modify the present invention described herein and still achieve the advantageous effects of the present invention. Therefore,...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More