Complementary metal oxide semiconductor (CMOS) circuit structure and manufacture method and display device thereof

A circuit structure and semiconductor technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems of complex production process, high production cost, increase production cost, etc., to simplify production process, reduce production cost, and prolong service life. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

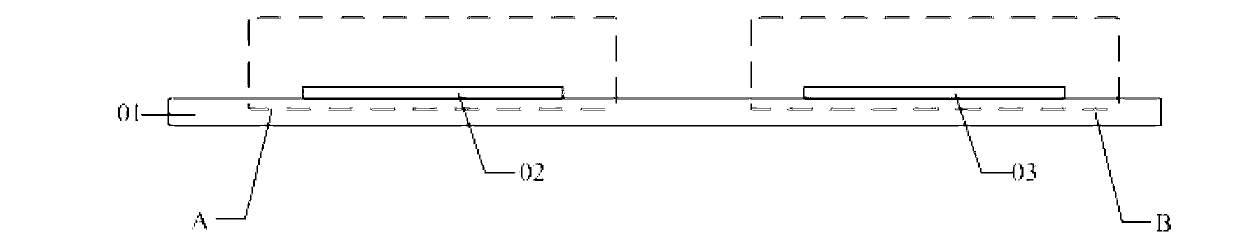

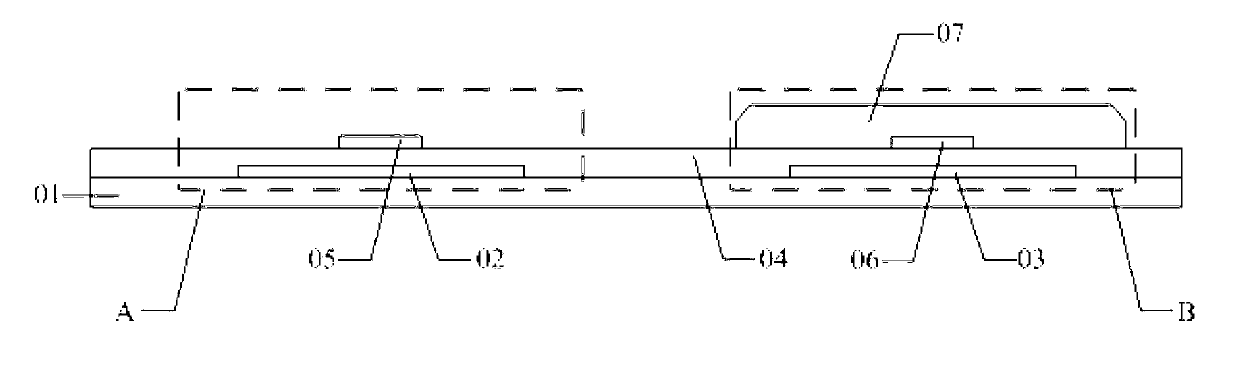

[0035] The specific implementation manners of the CMOS circuit structure provided by the embodiments of the present invention, its manufacturing method and the display device will be described in detail below with reference to the accompanying drawings.

[0036] The shape and size of each region in the drawings do not reflect the real scale of the CMOS circuit structure, but are only intended to schematically illustrate the content of the present invention.

[0037] A kind of CMOS circuit structure that the embodiment of the present invention provides, such as figure 2 As shown, there is a PMOS region C and an NMOS region D, including: a PMOS semiconductor layer 22, a gate insulating layer 23, a PMOS gate 24 and an NMOS gate 25, and a first interlayer dielectric layer 26 located on the base substrate 21 in sequence. , NMOS semiconductor layer 27, second interlayer dielectric layer 28, PMOS source and drain electrodes 29 and NMOS source and drain electrodes 30, wherein,

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More