Interconnect Fabrication Method

A manufacturing method and interconnection structure technology, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as damage to the outline of the low-k dielectric layer 100, reduction in the quality of metal wiring, and short-circuiting of devices. Reliability and electrical performance, avoiding copper filling voids, effect of good copper filling performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The method for manufacturing the interconnection structure proposed by the present invention will be further described in detail below with reference to the accompanying drawings and specific embodiments.

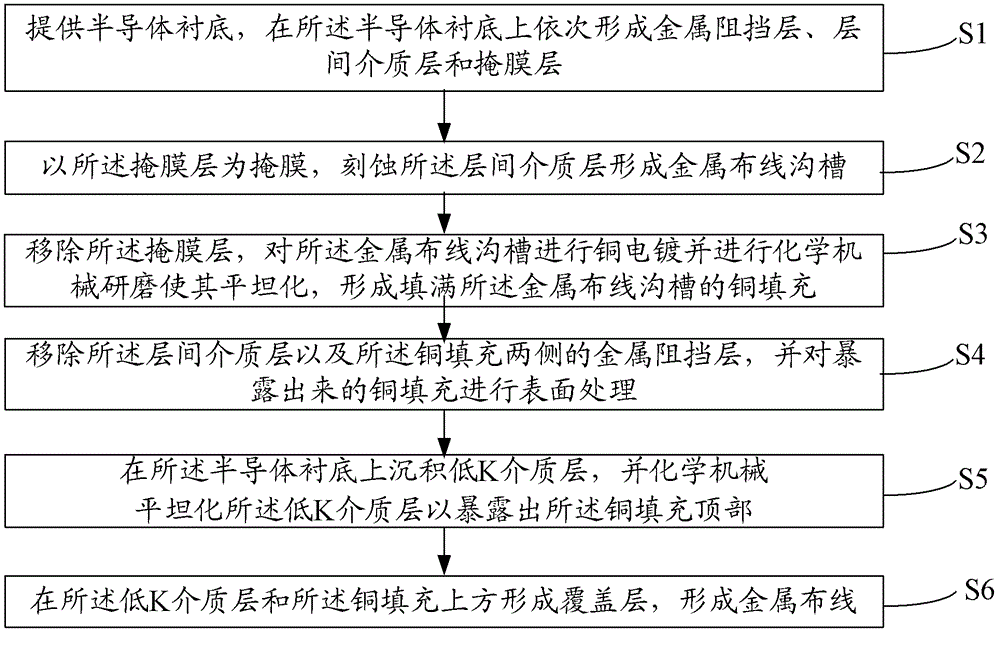

[0030] like figure 2 As shown, the present invention proposes a method for manufacturing an interconnection structure, comprising the following steps:

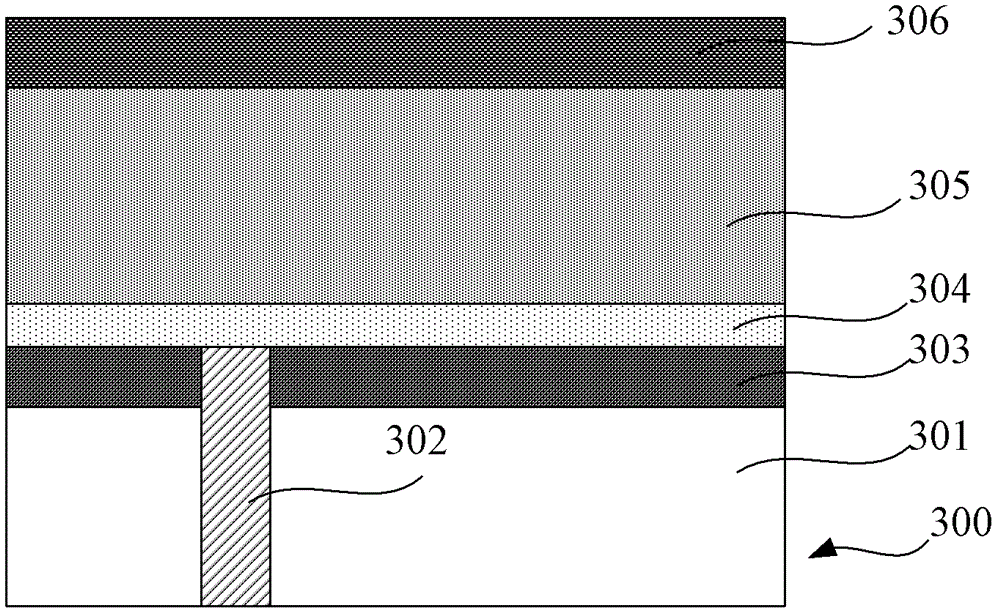

[0031] S1, providing a semiconductor substrate, and sequentially forming a metal barrier layer, an interlayer dielectric layer, and a mask layer on the semiconductor substrate;

[0032] S2, using the mask layer as a mask, etching the interlayer dielectric layer to form metal wiring trenches;

[0033] S3, removing the mask layer, performing copper electroplating on the metal wiring groove and performing chemical mechanical polishing to make it planarized, forming a copper filling that fills the metal wiring groove;

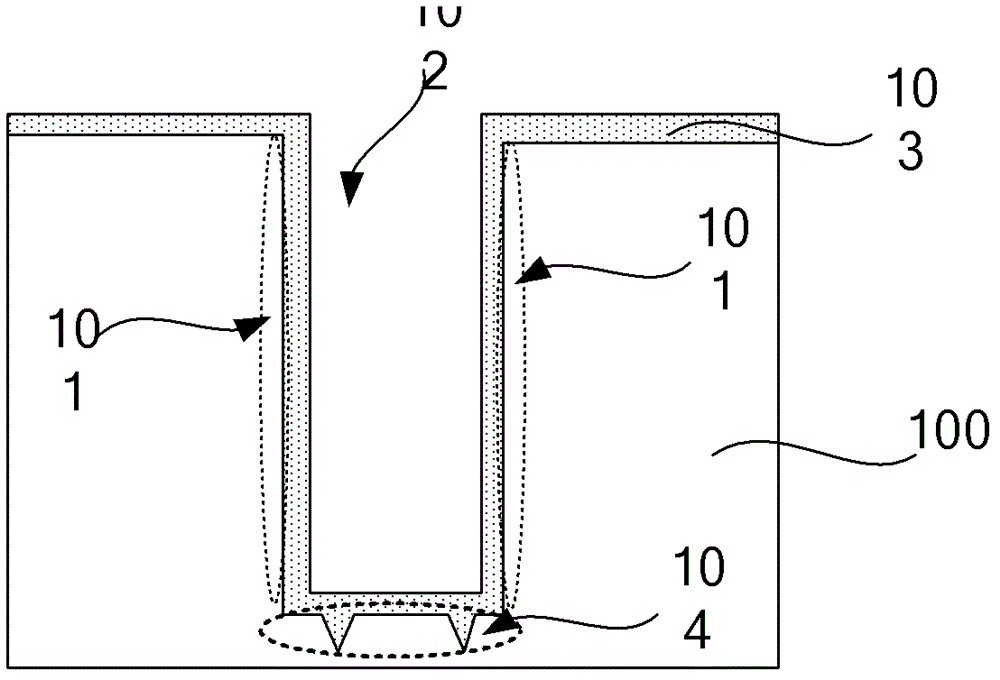

[0034] S4, removing the interlayer dielectric layer and the metal barrier layers on both sides of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More