Ultra-high voltage LDMOS (Laterally Diffused Metal Oxide Semiconductor) device structure and production method thereof

A device structure and ultra-high voltage technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of difficult to weaken the surface electric field in the drift region and the device is easy to be broken down, so as to increase the process steps and cost, The effect of increasing the breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

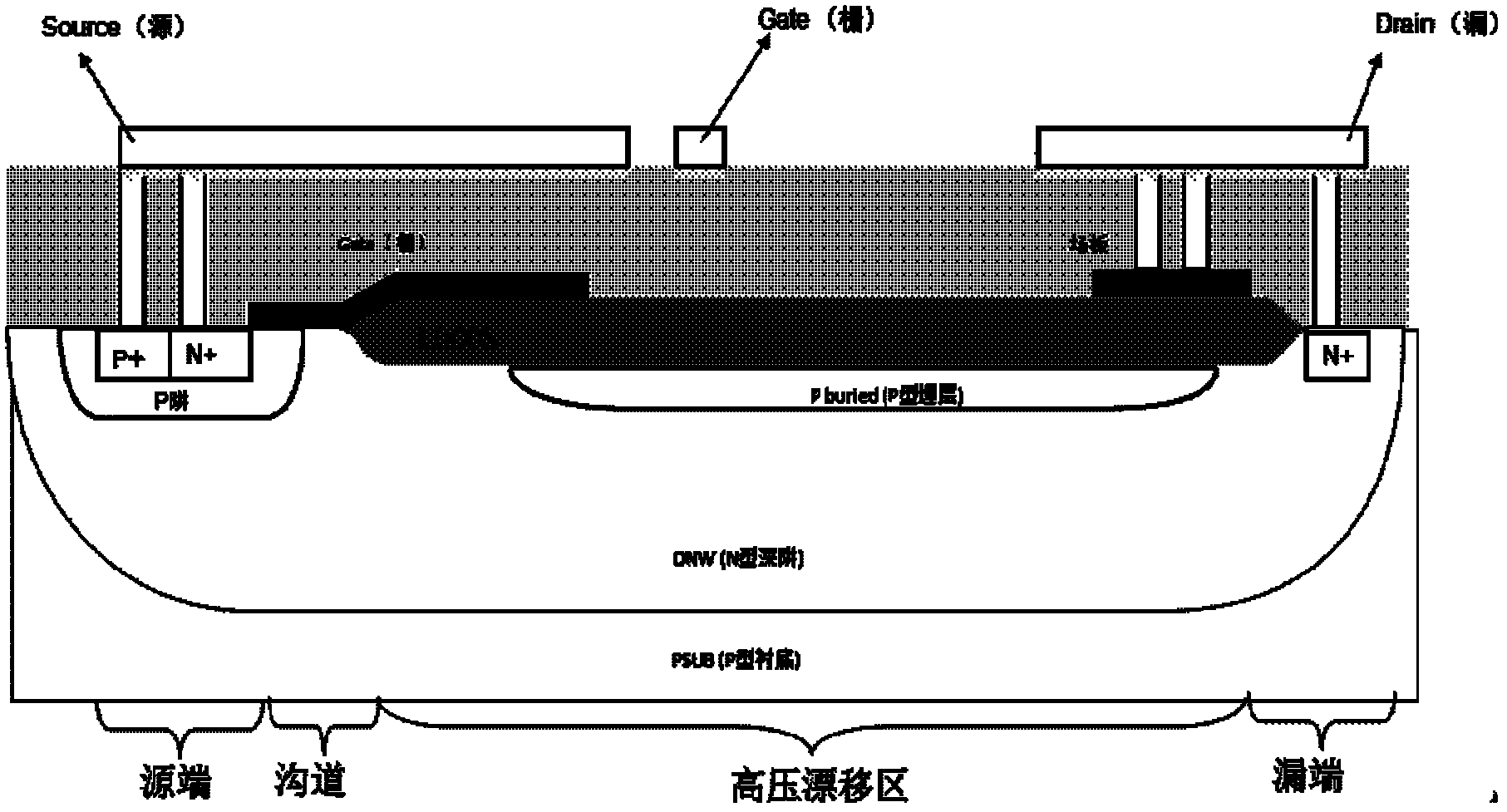

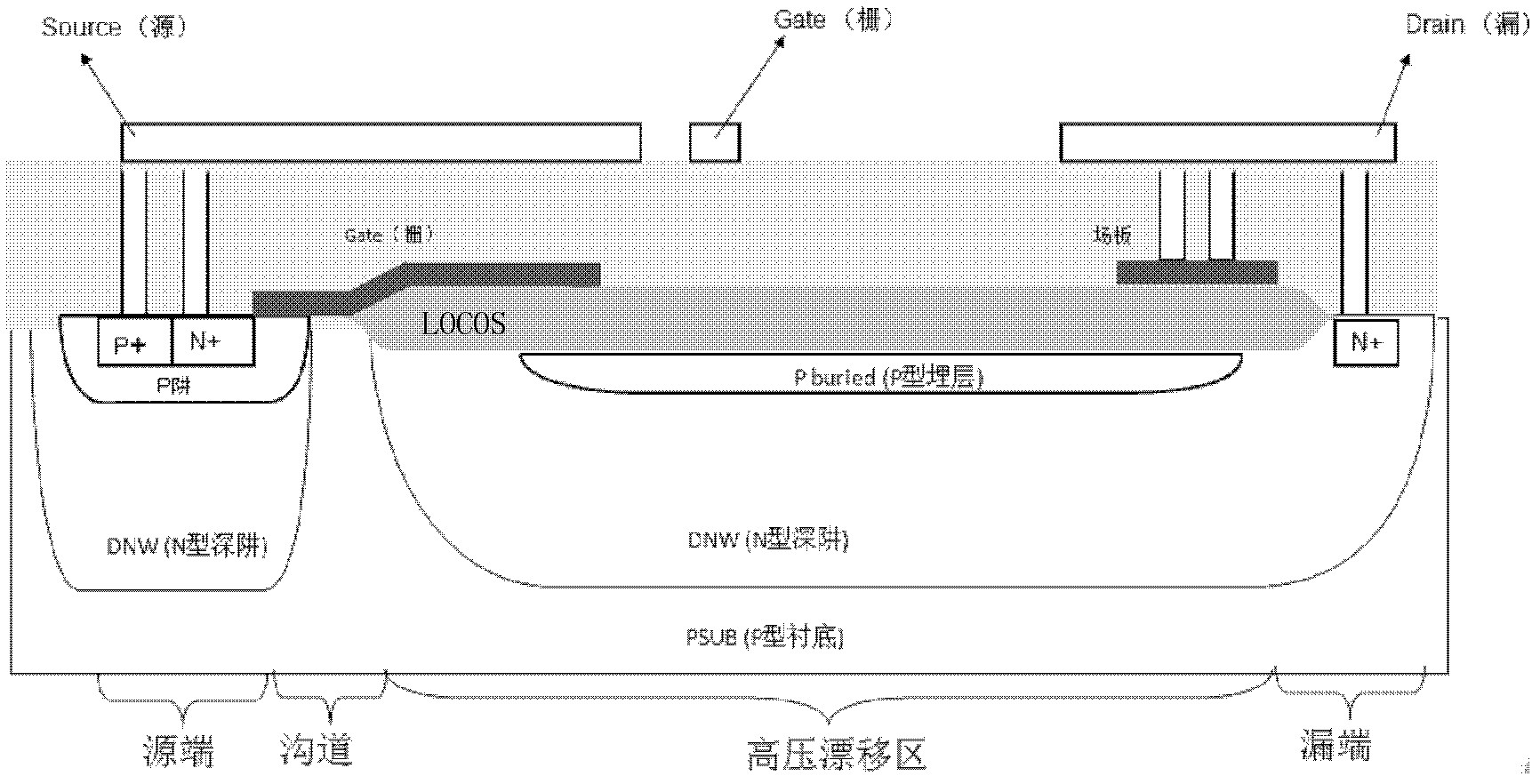

[0018] In order to have a more specific understanding of the technical content, characteristics and effects of the present invention, now taking the ultra-high voltage N-type LDMOS device as an example, combined with the illustrated embodiment, the technical solution of the present invention is described in detail as follows:

[0019] Such as image 3 As shown, the ultra-high-voltage LDMOS device of the embodiment of the present invention has two N-type deep wells (DNW), wherein, a P well (PW) for the source end of the LDMOS device is placed in one DNW, and a drain end withstand voltage is placed in the other DNW. The P-type buried layer (P buried); the two deep N wells are separated by a P-type substrate (PSUB).

[0020] The preparation method of the ultra-high voltage LDMOS device with the above structure is as follows:

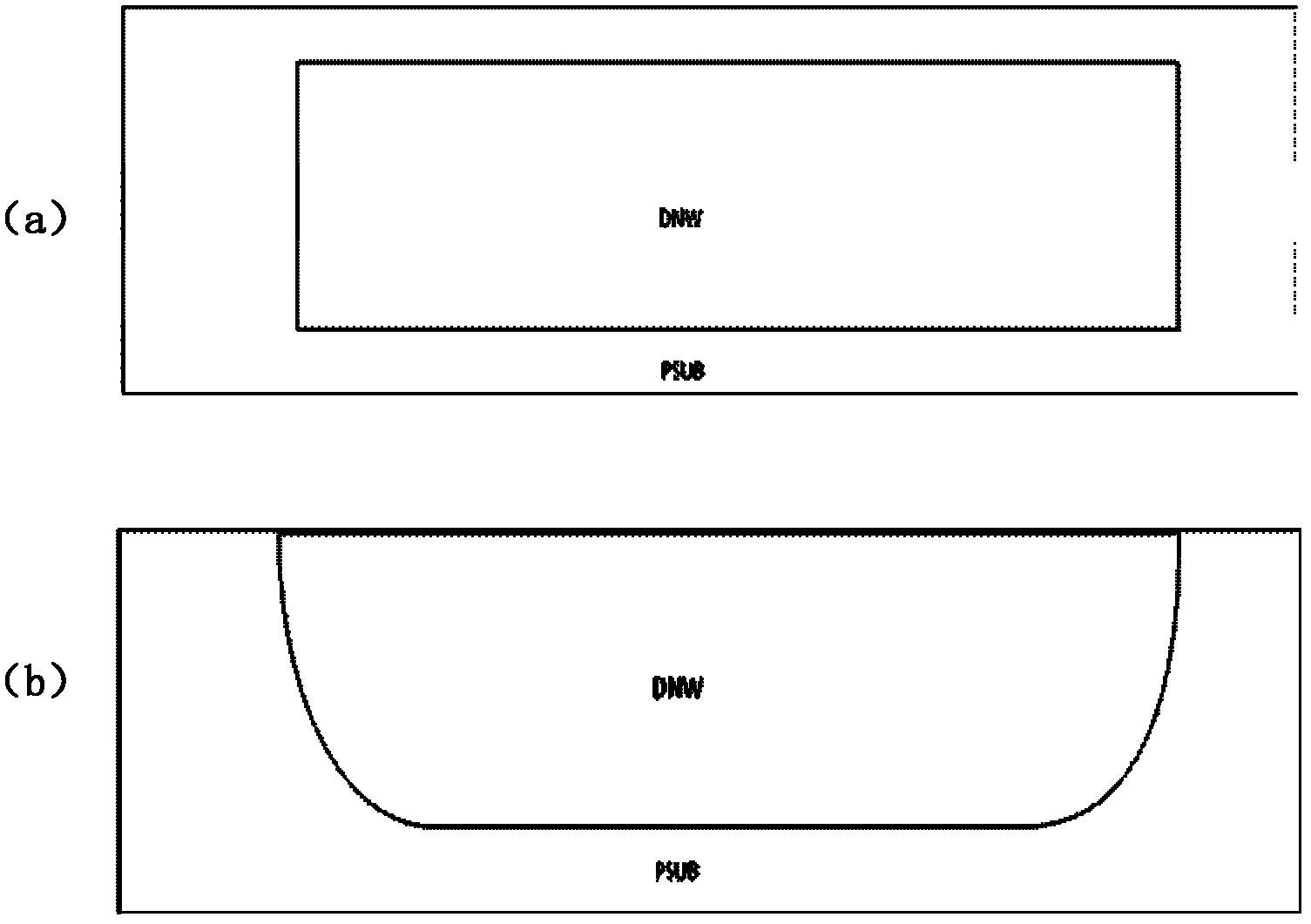

[0021] Step 1, design the mask plate of the DNW of the LDMOS device, and inject the traditional DNW into the pattern (such as figure 2 shown) changed to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More