Method for preparing N-type substrate microcrystalline silicon hetero-junction cell based on SE selective emitter junction

A heterojunction cell, selective technology, applied in circuits, electrical components, climate sustainability, etc., can solve the problems of difficult passivation of silicon wafers, low photoelectric conversion rate, etc., to improve photoelectric conversion rate and low cost , easily compatible effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

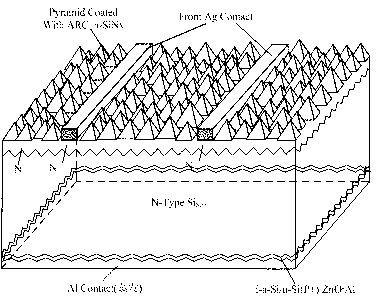

Image

Examples

Embodiment 1

[0023] Example 1: (1) Cleaning the silicon wafer substrate for texturing: first use NaOH solution to remove the damaged layer of the silicon wafer substrate; then use KOH solution, isopropyl alcohol IPA and texturing additives to etch the textured surface; After soaking in HCL solution, rinse with deionized water and dry.

[0024] (2) Print phosphor ink on the front side of the silicon wafer through a screen and dry it: on the special SE phosphor ink screen, use screen printing technology to transfer the phosphor ink to the N-type silicon wafer substrate, and dry it for use .

[0025] (3) Then diffuse the silicon wafer to form a selective emission junction N+ diffusion layer on the front side of the silicon wafer: put the silicon wafer substrate into the diffusion furnace, and perform one-time diffusion with phosphorus oxychloride as the liquid diffusion source. The temperature of the diffusion furnace is controlled at 820° C., and the diffusion time is 25 minutes, so that th...

Embodiment 2

[0032] Example 2: (1) First use NaOH solution to remove the damaged layer of the silicon wafer substrate; then use KOH solution, isopropanol IPA and texturing additives to etch the textured surface, and finally soak in HCL solution, then use deionized water Rinse, dry.

[0033] (2) On the special SE phosphor ink screen, use screen printing technology to transfer the phosphor ink to the N-type silicon wafer substrate, and dry it for use.

[0034] (3) Put the silicon wafer substrate into the diffusion furnace, and perform one-time diffusion with phosphorus oxychloride as the liquid diffusion source. The temperature of the diffusion furnace is controlled at 850° C., and the diffusion time is 30 minutes, so that the square resistance of the selective diffusion area is controlled at 75 ohm / square, and the surface resistance of the non-reexpanded area is controlled at 35 ohm / square.

[0035] (4) Secondary cleaning of silicon wafers.

[0036] (5) The N+ front of the battery is etch...

Embodiment 3

[0041] Example 3: (1) First use NaOH solution to remove the damaged layer of the silicon wafer substrate; then use KOH solution, isopropanol IPA and texturing additives to etch the textured surface, and finally soak in HCL solution, then use deionized water Rinse, dry.

[0042] (2) On the special SE phosphor ink screen, use screen printing technology to transfer the phosphor ink to the N-type silicon wafer substrate, and dry it for use.

[0043] (3) Put the silicon wafer substrate into the diffusion furnace, and perform one-time diffusion with phosphorus oxychloride as the liquid diffusion source. The temperature of the diffusion furnace is controlled at 860° C., and the diffusion time is 35 minutes, so that the square resistance of the selective diffusion area is controlled at 80 ohm / square, and the surface resistance of the non-reexpanded area is controlled at 40 ohm / square.

[0044] (4) Secondary cleaning of silicon wafers.

[0045] (5) The N+ front of the battery is etch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More