Digital control oscillator and method, system and detector for hardware performance detection

A digitally controlled oscillation and hardware performance technology, applied in the electronic field, can solve the problems of high front-end and back-end requirements of chip design, long lock-up time, poor adaptability, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0095] See image 3 As shown in , it shows a schematic structural diagram of the hardware performance detector provided by Embodiment 1 of the present invention. The hardware performance detector 30 may include, but is not limited to: a control unit 31 , a digitally controlled oscillator 32 , a first frequency divider 33 , a second frequency divider 34 , a first counter 35 and a second counter 36 .

[0096] The control unit 31 is connected with the digitally controlled oscillator 32 so as to control the digitally controlled oscillator 32 to output an oscillation clock, and the oscillation clock is the clock signal output by the digitally controlled oscillator 32 .

[0097] The first frequency divider 33 divides the frequency of a predetermined reference clock to obtain a first frequency-divided clock, and the second frequency divider 34 divides the frequency of the oscillation clock output by the digitally controlled oscillator 32 to obtain a second frequency-divided clock. I...

Embodiment 2

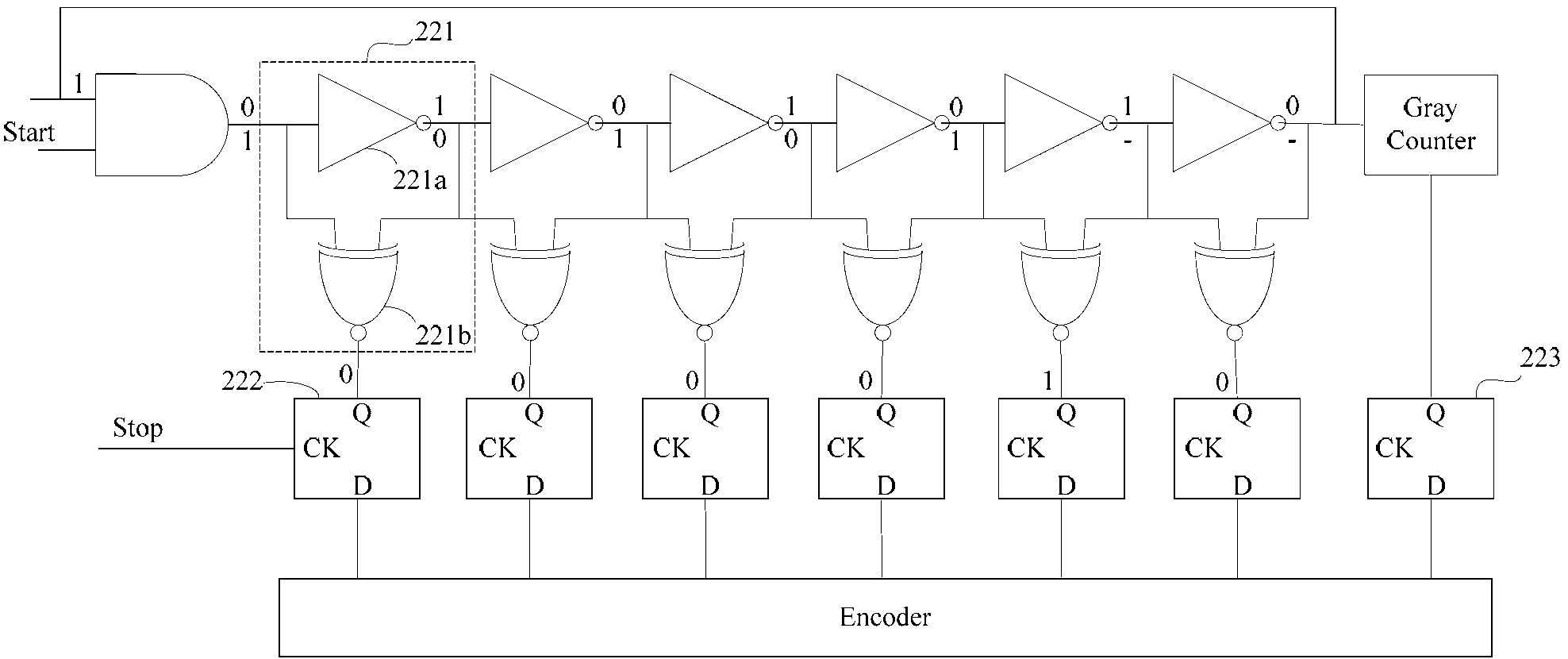

[0111] See Figure 4 As shown in FIG. 2 , it shows a schematic structural diagram of the digitally controlled oscillator in the hardware performance detector provided by Embodiment 2 of the present invention. The digitally controlled oscillator can be figure 1 The digitally controlled oscillator 32 shown in FIG. 2 may include: a NAND gate 410 , a first delay chain 420 , a second delay chain 430 and a NOT gate 440 .

[0112] The first delay chain 420 is formed by cascading at least two first delay units, such as Figure 4 As shown, the first delay chain 420 includes a plurality of cascaded first delay units such as the first delay unit 420a, the first delay unit 420b, and the first delay unit 420c. The first delay chain 420 may receive the first group selection signal sent by the control unit 31, and determine the effective first delay unit in the first delay chain 420 according to the first group selection signal. Wherein, the first group of selection signals is a group of ...

Embodiment 3

[0129] See Figure 5 As shown, it shows a method flow chart of the hardware performance detection method provided by Embodiment 3 of the present invention. The hardware performance detection method may include:

[0130] 501. After receiving an operation signal, receive a predefined parameter signal and a reference clock;

[0131] In a specific application scenario, the hardware performance detection method also includes a calibration process before step 501, and the predefined parameter signal can be obtained through the calibration process. The calibration process can include:

[0132] First, after receiving the calibration signal, receive the ratio signal and the reference clock;

[0133] Usually, the mode selection module 311 in the control unit 31 receives the calibration signal, indicating that the hardware performance detector 30 enters the calibration mode. In entering the calibration mode, the hardware performance detector 30 receives the ratio signal and the refer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More