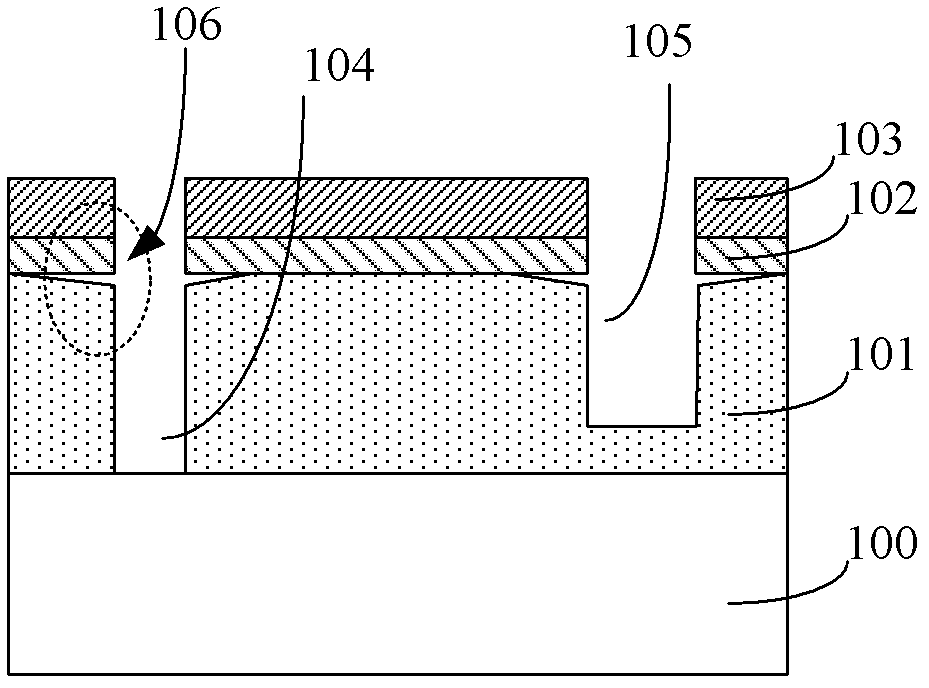

Hard mask layer structure, manufacturing method thereof and manufacturing method of semiconductor device

A device manufacturing method and hard mask layer technology, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as disconnection, affecting copper filling performance, and easy to be peeled off, so as to increase the process window, Avoid undercut damage and improve the effect of carbon loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The manufacturing method of the semiconductor device proposed by the present invention will be further described in detail below with reference to the accompanying drawings and specific embodiments.

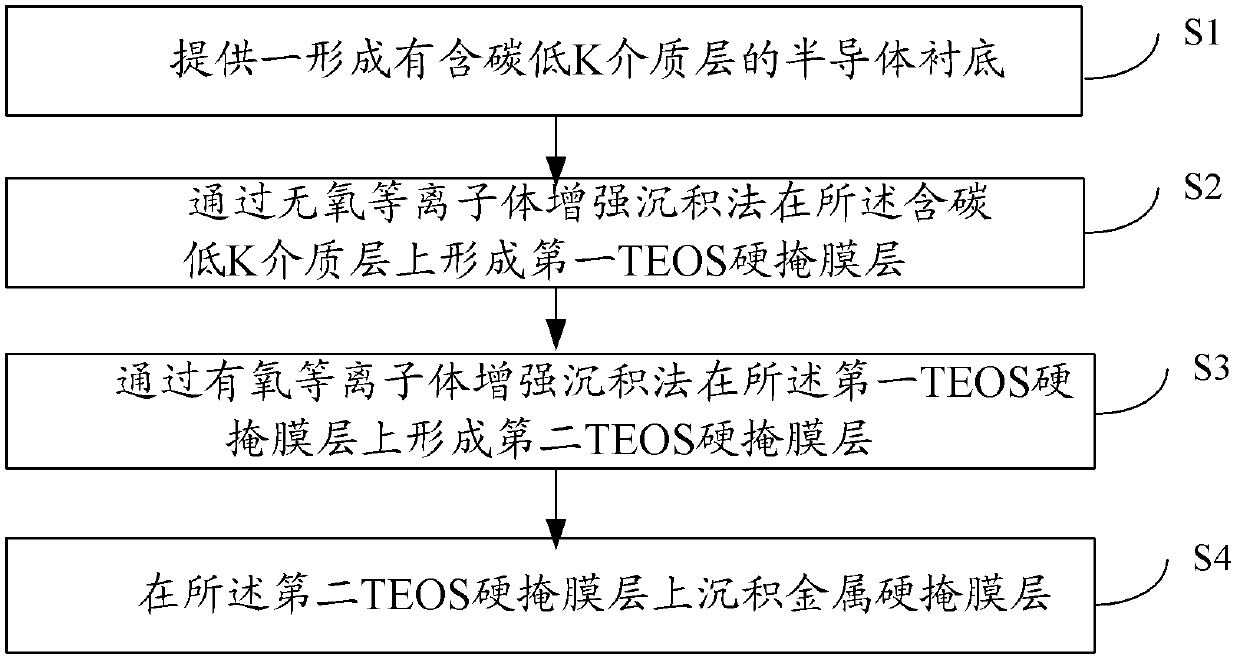

[0025] Such as figure 2 As shown, the present invention provides a method for manufacturing a hard mask layer structure, comprising the following steps:

[0026] S1, providing a semiconductor substrate formed with a carbon-containing low-K dielectric layer;

[0027] S2, forming a first TEOS hard mask layer on the carbon-containing low-K dielectric layer by an oxygen-free plasma enhanced deposition method;

[0028] S3, forming a second TEOS hard mask layer on the first TEOS hard mask layer by an oxygen plasma enhanced deposition method;

[0029] S4, depositing a metal hard mask layer on the second TEOS hard mask layer.

[0030] Please refer to Figure 3A , in step S1, the provided semiconductor substrate 300 may be a silicon substrate, a silicon-on-insulator substrate,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More