Method for forming semiconductor structure

A technology of semiconductor and plasma, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc. It can solve the problems of poor morphology of conductive plugs, uneven size of through holes, open circuit of conductive plugs, etc. It is difficult to achieve the size, Improved reactivity and precise opening size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

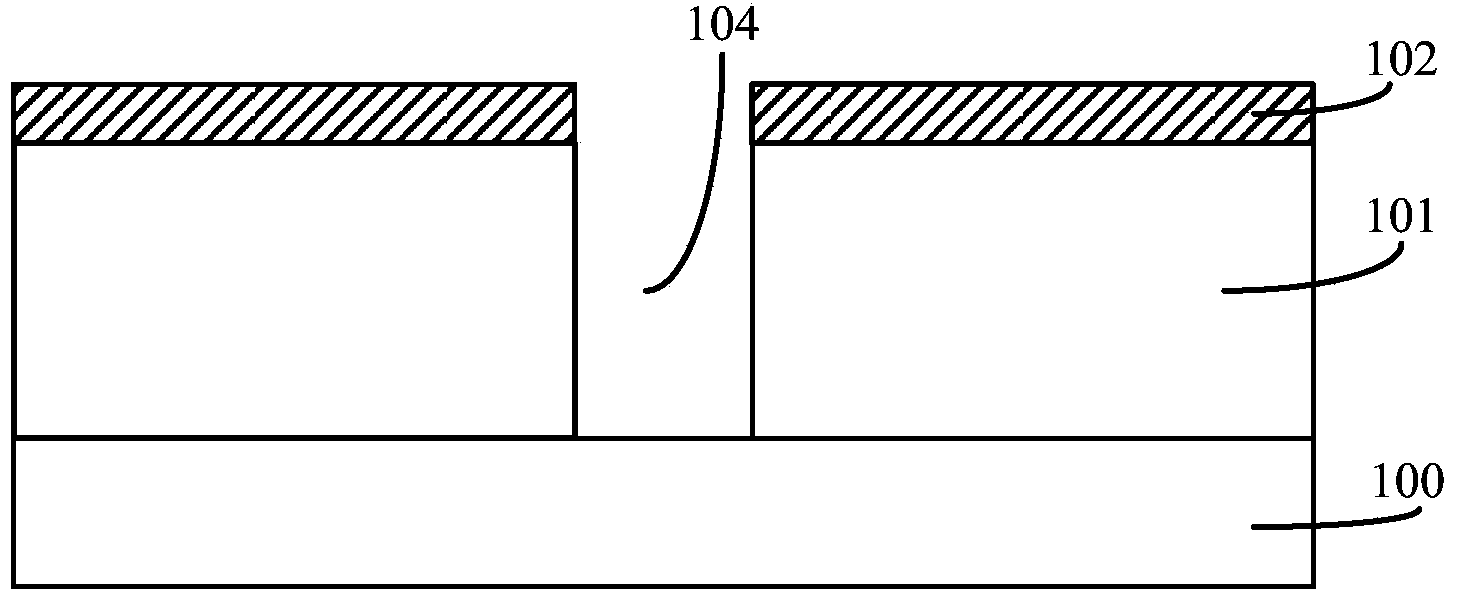

[0048] Figure 3 to Figure 6 is a schematic diagram of the formation process of the semiconductor structure according to the first embodiment of the present invention.

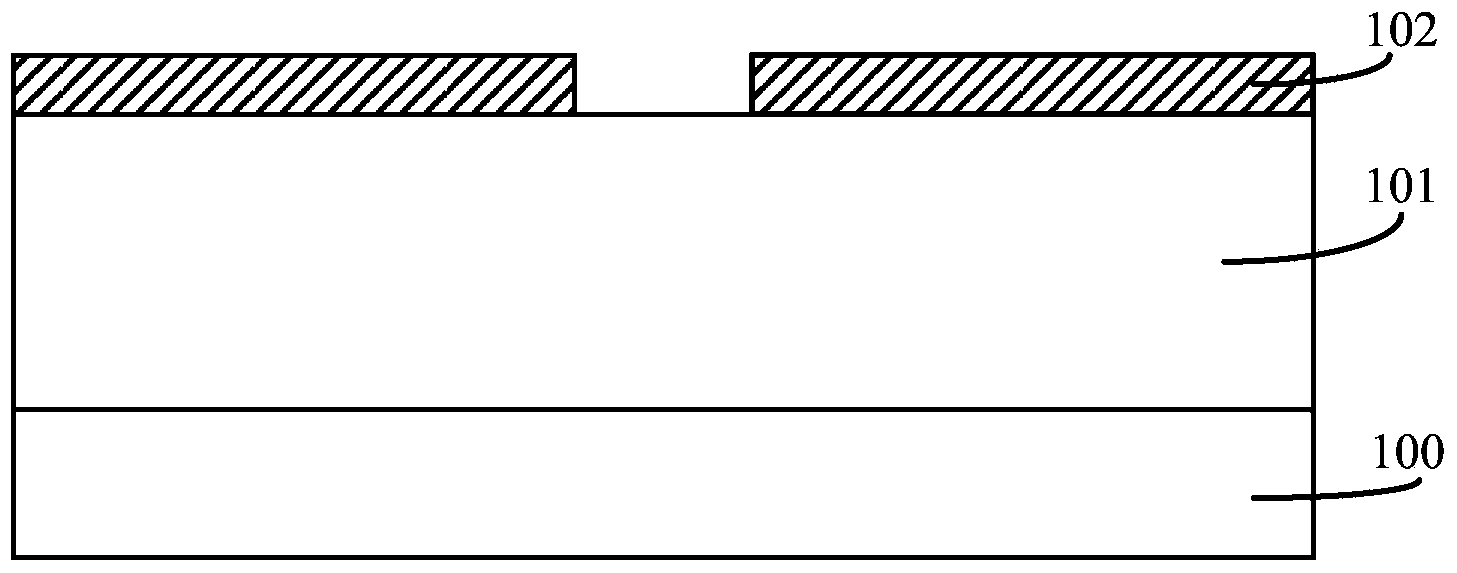

[0049] Please refer to image 3 A substrate 200 is provided, the surface of the substrate 200 has a layer to be etched 201 ; a mask layer 202 is formed on the surface of the layer to be etched 201 , and the mask layer 202 exposes a part of the surface of the layer to be etched 201 .

[0050] In this embodiment, the base 200 includes a semiconductor substrate, a semiconductor device formed on the surface of the semiconductor substrate or formed in the semiconductor substrate, a conductive structure for electrically connecting the semiconductor device, and a The insulating layer of the semiconductor device and the conductive structure. The semiconductor substrate includes a silicon substrate, a silicon germanium substrate, a silicon carbide substrate, a silicon-on-insulator substrate, a germanium-on-insulator ...

no. 2 example

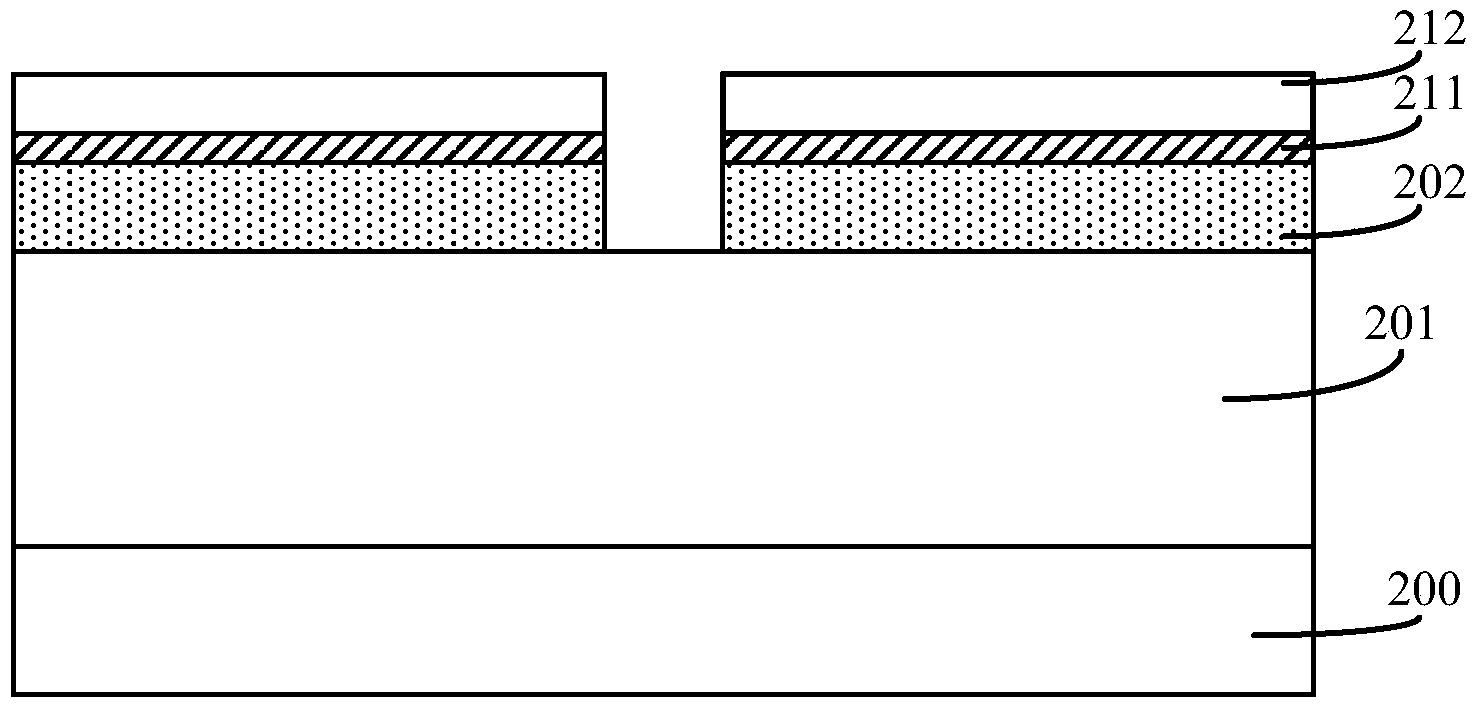

[0096] Figure 15 to Figure 16 is a schematic diagram of the formation process of the semiconductor structure according to the second embodiment of the present invention.

[0097] Please refer to Figure 15 , providing a substrate 300, the surface of the substrate 300 has a layer to be etched 301; a mask layer 302 is formed on the surface of the layer to be etched 301, and the mask layer 302 exposes a part of the surface of the layer to be etched 301, the The material of the mask layer 302 is amorphous carbon.

[0098] The structure, material and formation process of the base 300 and the mask layer 302 are the same as those described in the first embodiment, and will not be repeated here. In addition, in this embodiment, the bottom anti-reflection layer 311 is formed on the surface of the mask layer 302, and the photoresist layer 312 on the surface of the bottom anti-reflection layer 311, the photoresist layer 312 exposes the subsequent The corresponding position of the ope...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Pulse frequency | aaaaa | aaaaa |

| Power | aaaaa | aaaaa |

| Power | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More