Semiconductor component with dual connection channels between interposer and coreless substrate

A coreless substrate, semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., to achieve the effects of high reliability, cost reduction, and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

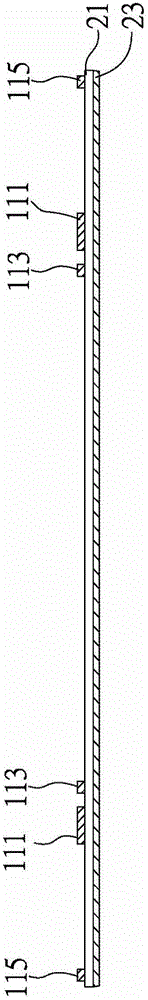

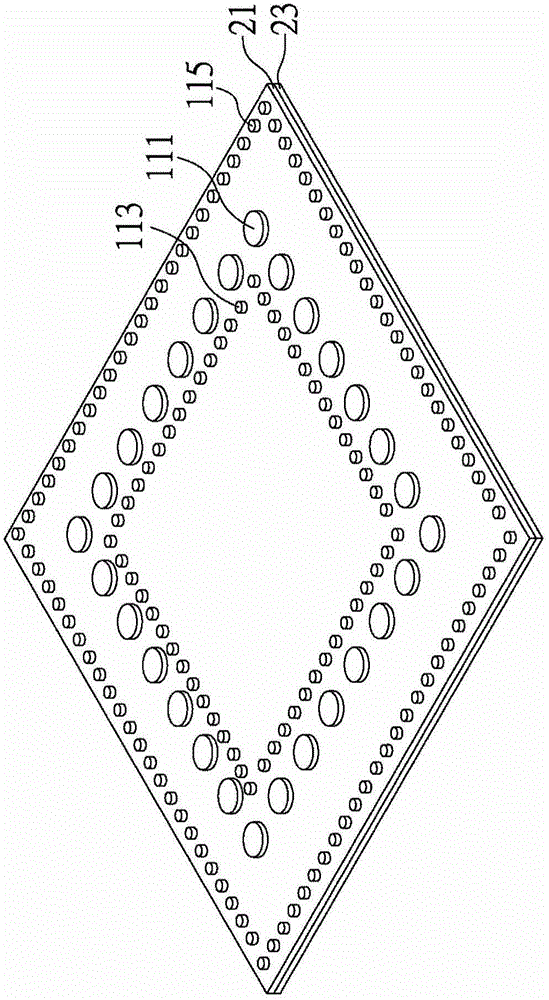

[0045] Figures 1A-1J According to an implementation aspect of the present invention, a method for manufacturing a semiconductor component, the semiconductor component includes an interposer, a semiconductor chip, a reinforcement layer, and a coreless substrate, and the coreless substrate is connected through wire bonding and conductive micro-holes. electrically connected to the interposer.

[0046] Such as Figure 1JAs shown, the semiconductor component 110 includes an interposer 31 , a strengthening layer 41 , a semiconductor chip 51 , a coreless substrate 20 , and wire bonding 321 . The interposer 31 includes a first surface 311 , a second surface 313 opposite to the first surface 311 , a first contact pad 312 and bonding fingers 316 on the first surface 311 , and a second contact pad 314 on the second surface 313 , the conductive via 318 partially connected to the first contact pad 312 and the second contact pad 314 , and the lateral circuit 320 electrically connected to ...

Embodiment 2

[0066] figure 2 Another three-dimensional device 310 according to another embodiment of the present invention has an additional first conductive microhole 243 in direct contact with the interposer 41 for grounding or electrical connection with passive components. figure 2 The sealing material 71 and the heat sink 81 are also shown in . The sealing material 71 (such as molding compound) fills the via hole 411 in an upward direction and covers the connection pad 111 , the spacer 113 , the first dielectric layer 21 , and the interposer 31 . A heat sink 81 (such as copper or aluminum) is attached to the reinforcement layer 41 and the semiconductor chip 51 via a thermally conductive adhesive 801 to assist heat dissipation, and the heat sink 81 covers the reinforcement layer 41 , the sealing material 71 , and the semiconductor chip 51 in an upward direction.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More