A high-voltage esd protection device with double anti-latch-up ring ldmos-scr structure

A LDMOS-SCR, ESD protection technology, applied in electric solid devices, semiconductor devices, electrical components, etc., can solve the problems of low trigger voltage, weak anti-latch ability, etc., achieve low trigger voltage, increase area, improve maintenance The effect of voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

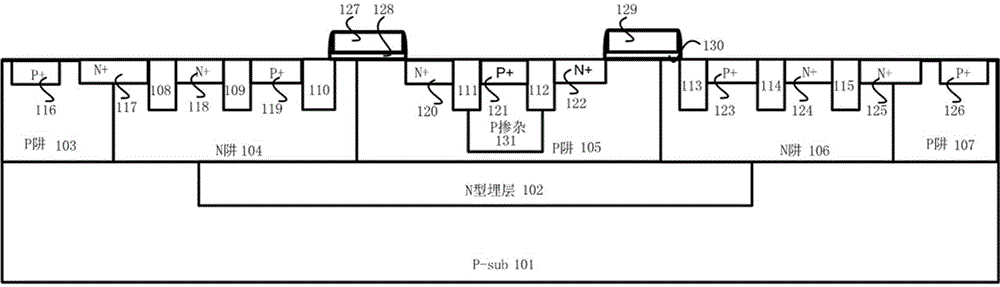

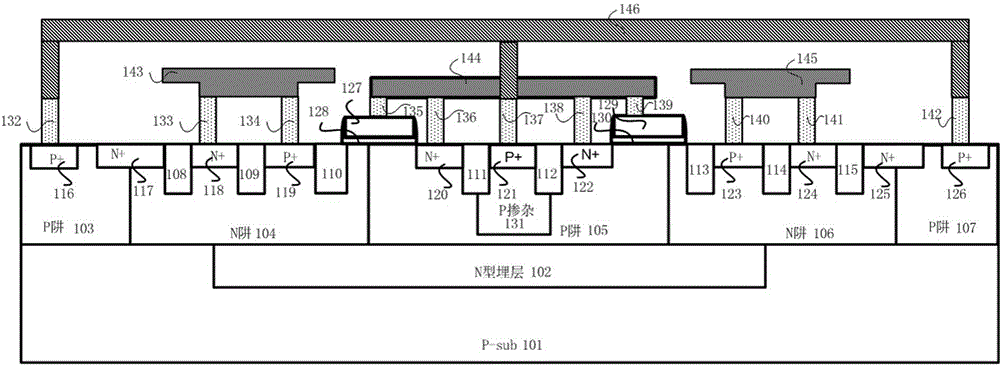

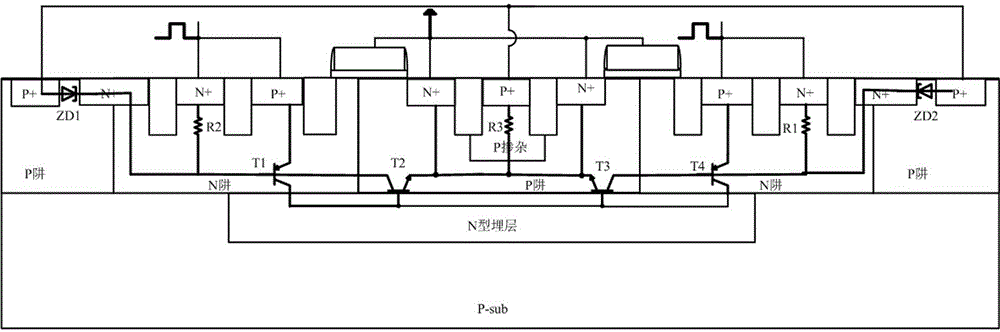

[0027] The present invention proposes a high-voltage ESD protection device with a double anti-latch-up annular LDMOS-SCR structure. Because it is mainly used in the field of high-voltage ESD protection, it needs to be based on a high-voltage BCD process platform, through reasonable design and control of certain features of the device layout parameters, ESD protection devices with different specifications that can meet various high-voltage ESD protection requirements can be prepared.

[0028] A high-voltage ESD protection device with double anti-latch-up annular LDMOS-SCR structure, which includes the ESD current discharge path of the LDMOS-SCR structure and the ESD current discharge path of Zener breakdown, and the layout of the annular LDMOS-SCR structure designed to increase hold voltage, hold current, and enhance ESD robustness of the device. It is characterized by: including P-type substrate 101, N-type buried layer 102, first P well 103, first N well 104, second P well 105,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More