Layering and reconfigurable on-chip network modeling and simulation system

A network-on-chip and simulation system technology, which is applied in the field of hierarchical and reconfigurable network-on-chip modeling and simulation systems, can solve problems such as inability to study details of network-on-chip design, deviation between evaluation results and actual conditions, and high abstraction levels, and achieve fast Modeling and performance simulation, accurate and comprehensive performance evaluation, and the effect of improving versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Hereinafter, the present invention will be described in detail through specific embodiments in conjunction with the accompanying drawings.

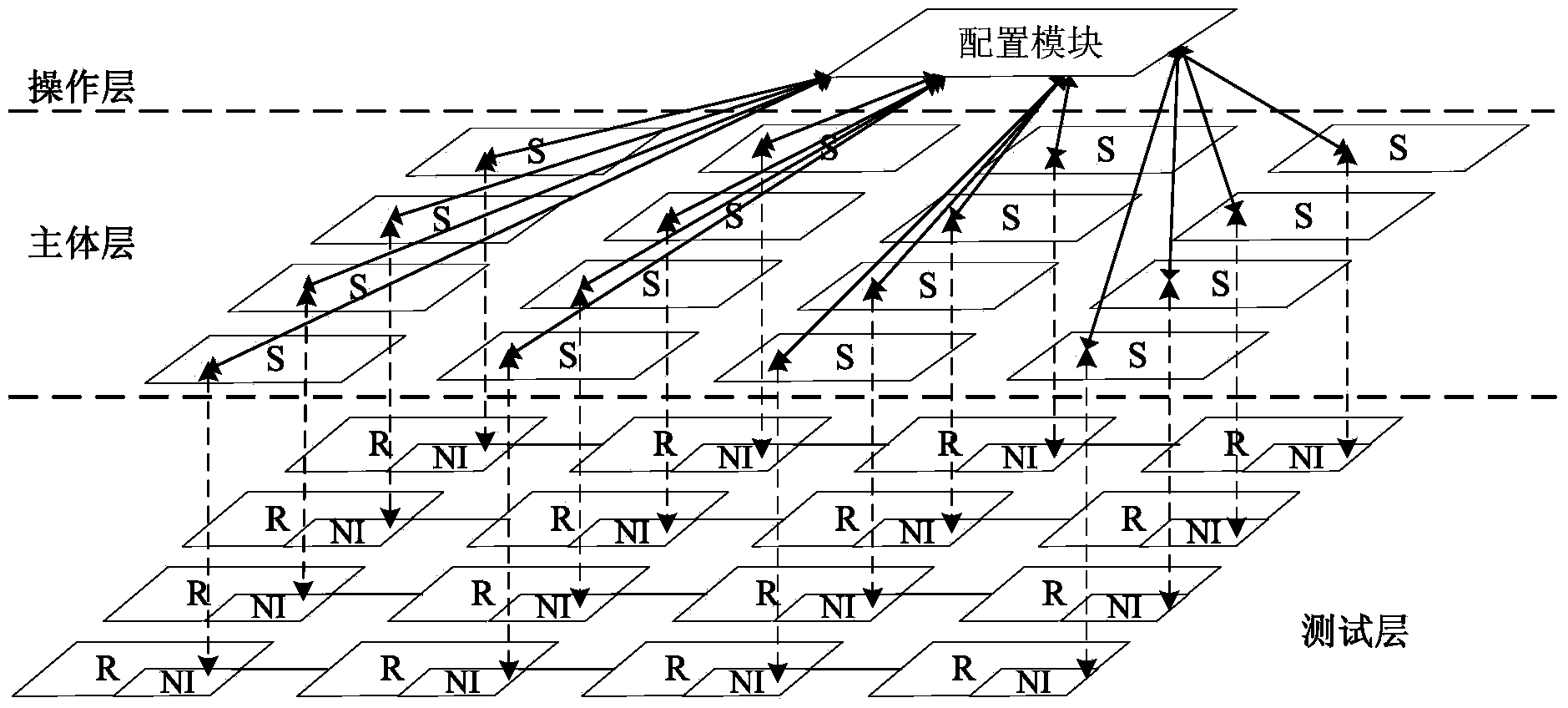

[0029] The hierarchical and reconfigurable network-on-chip simulation system of the present invention includes three layers: an operation layer, a main body layer, and a test layer, and is used for modeling key characteristics of the network-on-chip and statistically analyzing performance indicators. Its structure is as follows: figure 1 shown. The functional composition and relationship of each layer are described as follows.

[0030] (1) The operation layer, which is directly oriented to the users of the simulation platform. Users interact with the simulation model through the software configuration module, set the network topology, network scale, routing algorithm, etc. The distribution model, data packet length, network injection rate, microchip size, etc. are convenient for testing various performance indicators of the on-chi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More