Method for improving reliability of gate oxide layer of peripheral circuit area of flash memory

A flash memory, peripheral circuit area technology, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of reduced gate oxide integrity and uniformity, reduced gate oxide reliability, and device doping profile offset. , resulting in improved reliability, ease of implementation, increased integrity and uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

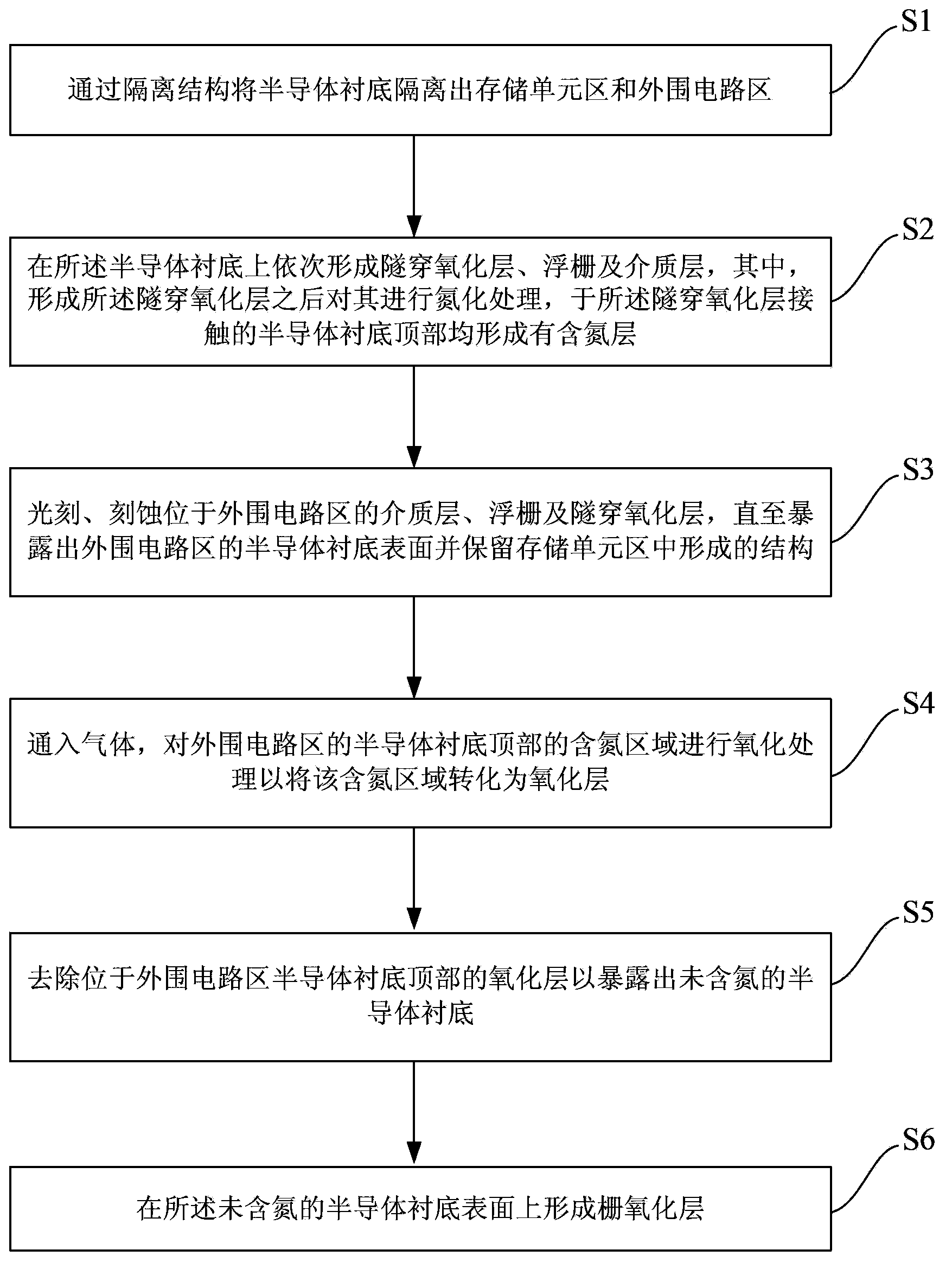

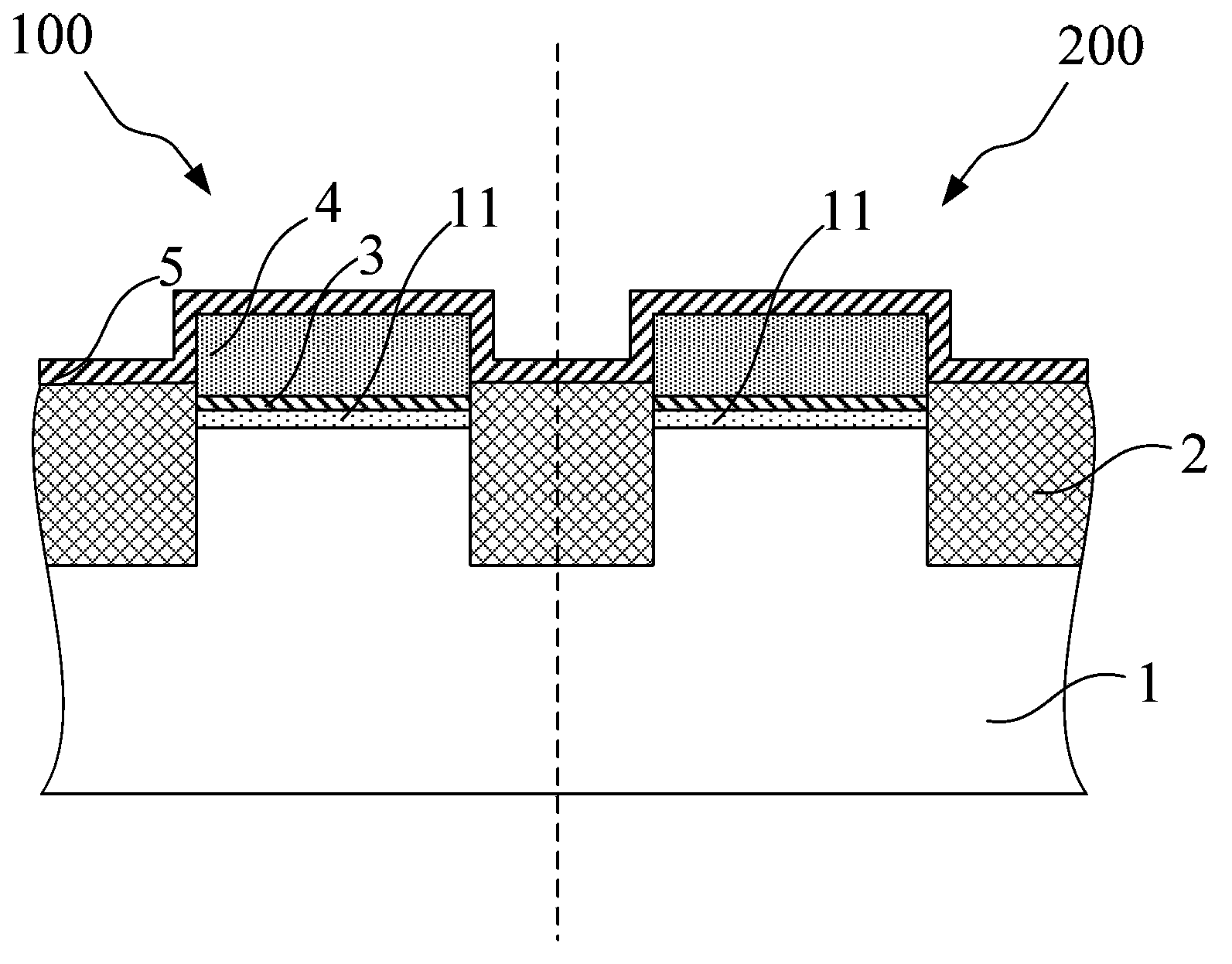

[0041] Such as Figure 1 to Figure 6 As shown, the present invention provides a method for improving the reliability of the gate oxide layer in the peripheral circuit region of the flash memory, and the method at least includes the following steps:

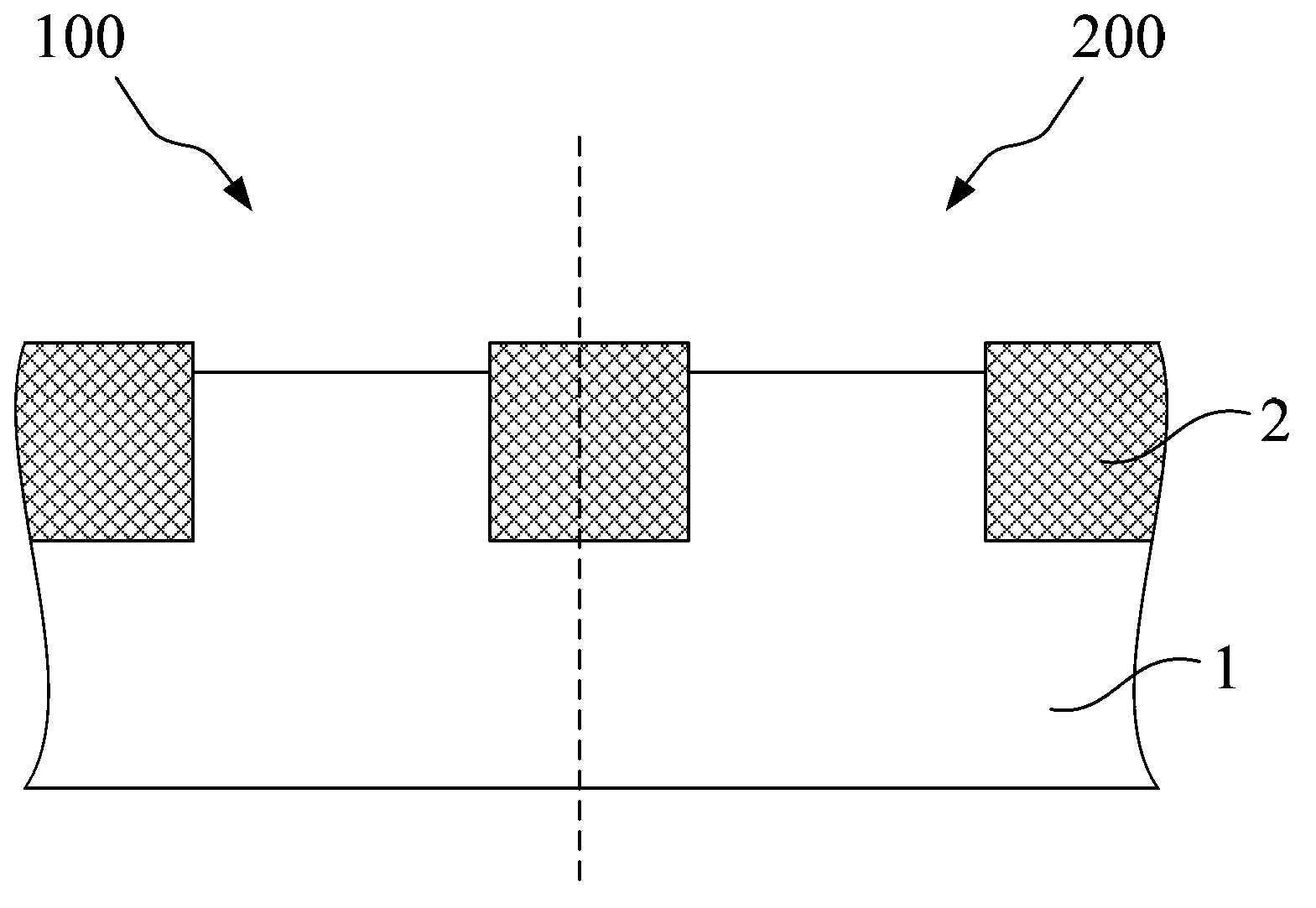

[0042] Do step 1) first, see figure 1 In step S1 and figure 2 , provide a semiconductor substrate 1 , and isolate the semiconductor substrate 1 from the memory cell region 100 and the peripheral circuit region 200 through the isolation structure 2 .

[0043] It should be pointed out that the specific steps of preparing shallow trench isolation 2 are: etching isolation trenches arranged in parallel on the semiconductor substrate formed with a hard mask, and then filling and planarizing the isolation trenches to achieve forming shallow trench isolation, wherein the surface of the shallow trench isolation is on the same plane as the surface of the hard mask on the semiconductor substrate, and then removing the hard mask to form ...

Embodiment 2

[0059]The scheme of embodiment 2 is basically the same as that of embodiment 1, the difference is only the gas introduced in step 4) and the relevant process conditions of oxidation treatment. For the rest of the same steps, please refer to the relevant description of embodiment 1, which will not be repeated here Let me repeat them one by one.

[0060] Firstly execute step 1) to step 3), please refer to the first embodiment for details. Then go to step 4).

[0061] In step 4) of Example 2, under the temperature condition of 100~150°C, H 2 SO 4 with H 2 o 2 The mixture (sulfuric peroxide mixture, SPM) gas is used to oxidize the nitrogen-containing region 11 on the top of the semiconductor substrate 1 in the peripheral circuit region 200 to convert the nitrogen-containing region 11 into an oxide layer 7 . Among them, H 2 SO 4 with H 2 o 2 The concentration ratio ranges from 5:1 to 7:1, and the thickness of the oxide layer is 50-100 angstroms. In the second embodiment, ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More