EPA (Ethernet for Plant Automation) communication IP (Intellectual Property) core and system on chip (SOC) based on AMBA (Advanced Microcontroller Bus Architecture) bus structure

A bus structure, system-on-chip technology, applied in bus network, general-purpose stored program computer, data exchange through path configuration, etc., can solve the problems of lack of reliability and stability, limited market prospects, expensive, etc., and achieve high integration. , the effect of broad security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

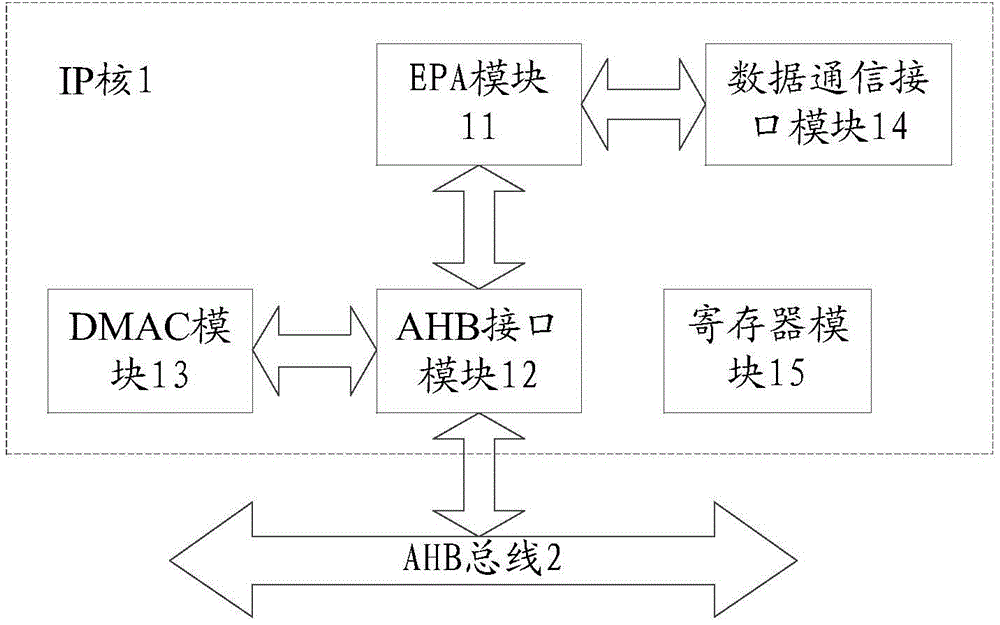

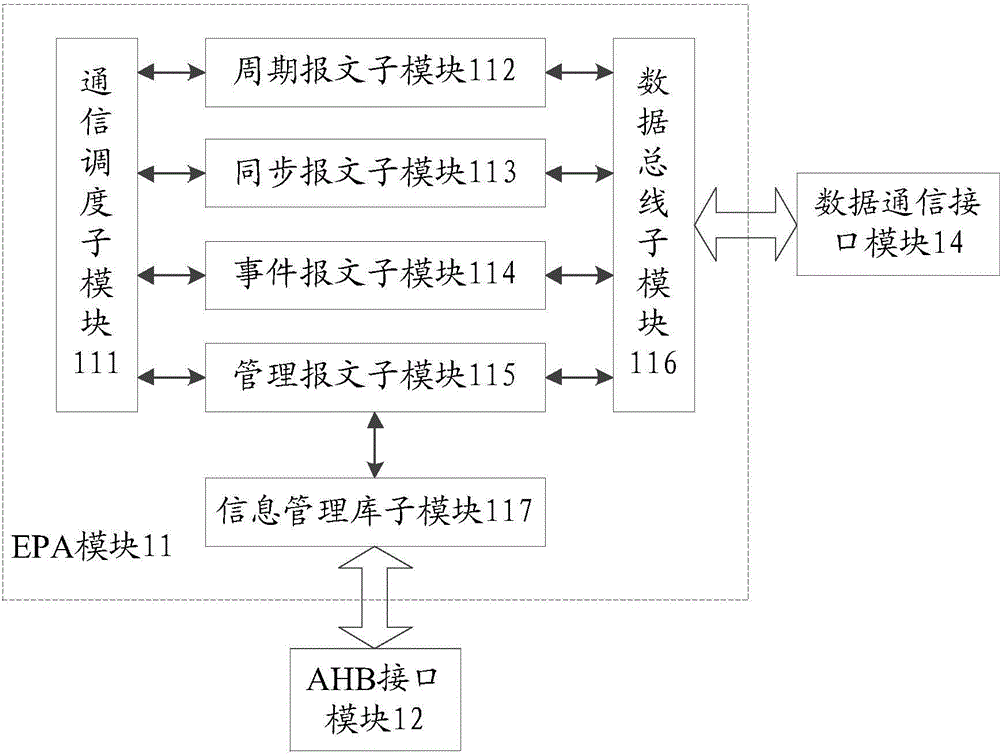

[0057] Such as figure 1 As shown, an EPA communication IP core based on the AMBA bus structure is used to connect to the AHB bus 2 of the system-on-chip to realize EPA communication. The IP core 1 includes:

[0058] The EPA module 11 is used to schedule and manage the sending and receiving of EPA communication messages;

[0059] The AHB interface module 12 is used to realize the communication connection between the IP core 1 and the AHB bus 2;

[0060] The DMAC module 13 is used to realize that the IP core 1 directly reads and writes the memory unit of the system on chip;

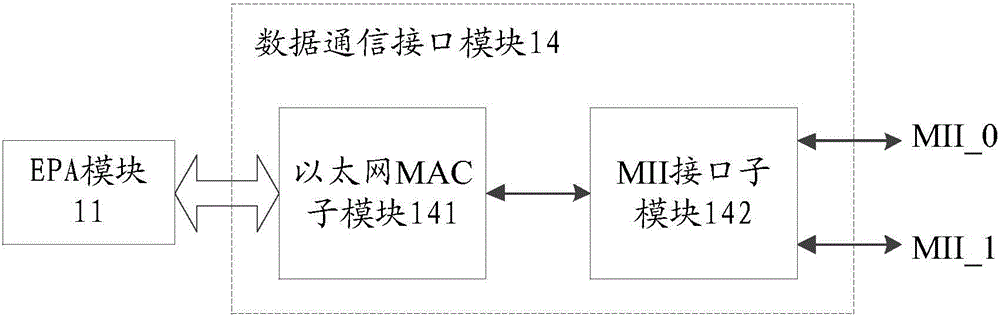

[0061] The data communication interface module 14 is used to build an EPA communication network to realize data interaction and communication between the IP core and an external host computer and other EPA devices; the data communication interface module 14 can be used to expand the communication network into star, line and different network topologies such as rings; and,

[0062] The register module 15...

Embodiment 2

[0078] Such as Figure 4 As shown, a kind of EPA communication system-on-chip based on AMBA bus structure comprises an AHB bus 2, and the AHB bus 2 is respectively mounted with:

[0079] The IP core 1 provided in Embodiment 1 is used to connect with an external host computer and periodically send and receive EPA communication messages. In this embodiment, two redundantly configured EPA modules 11 are used in the IP core 1 .

[0080] The memory unit 4 is used for storing configuration information of the IP core 1 and EPA communication message data. In this embodiment, the memory unit 4 includes a SRAM memory and a FLASH memory connected to the AHB bus 2 respectively; wherein, the FLASH memory is used to store configuration information, and the SRAM memory is used to store EPA communication message data.

[0081] The input and output unit 5 is used for connecting external devices. In this embodiment, the input and output unit 5 includes a GPIO interface, but is not limited th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More