A core-shell field-effect transistor and its preparation method

A technology of field effect transistor and core source, which is applied in the field of gate-around field effect transistor and its preparation, can solve the problem of small driving current, achieve the effect of increasing mobility, increasing driving current, and solving thermal stability problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

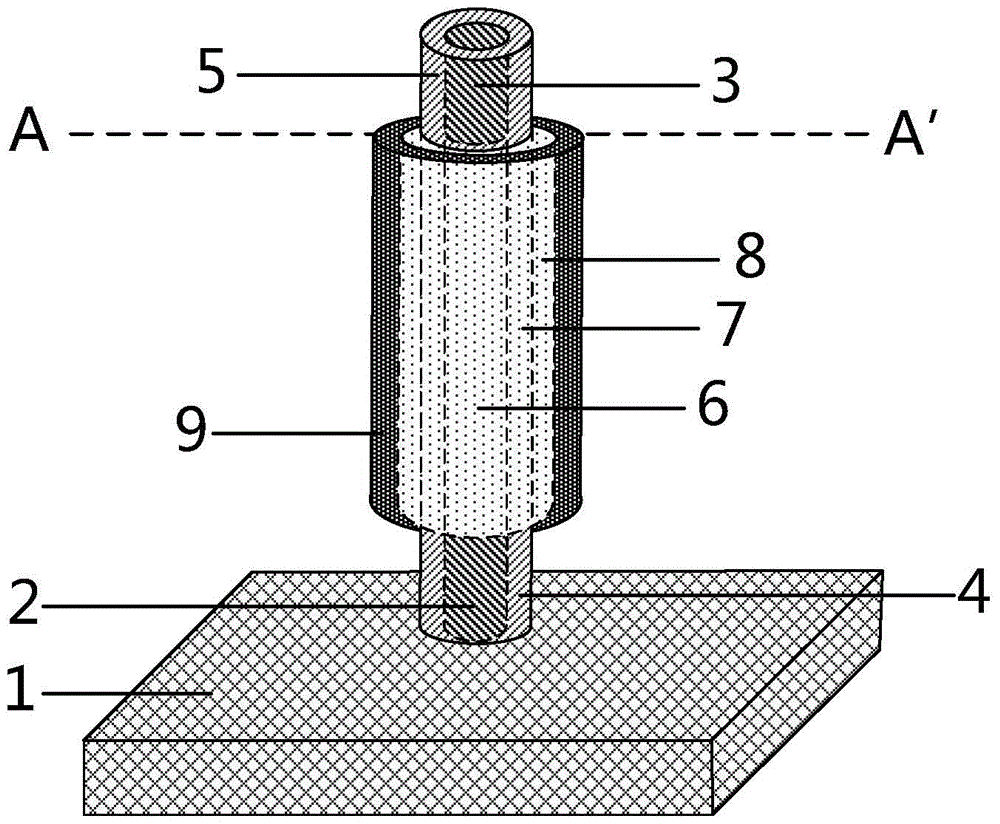

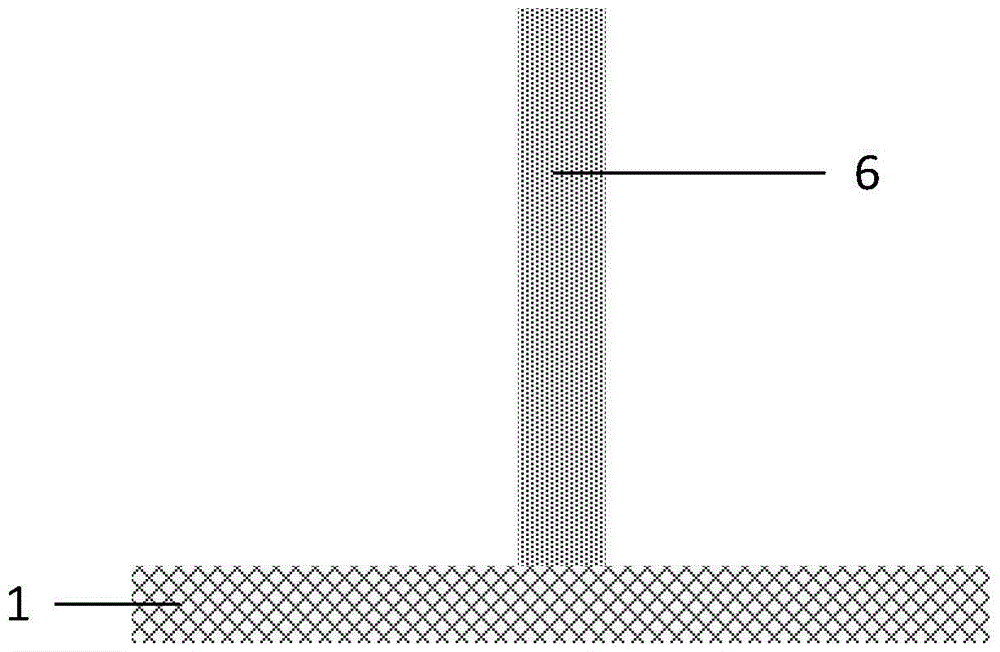

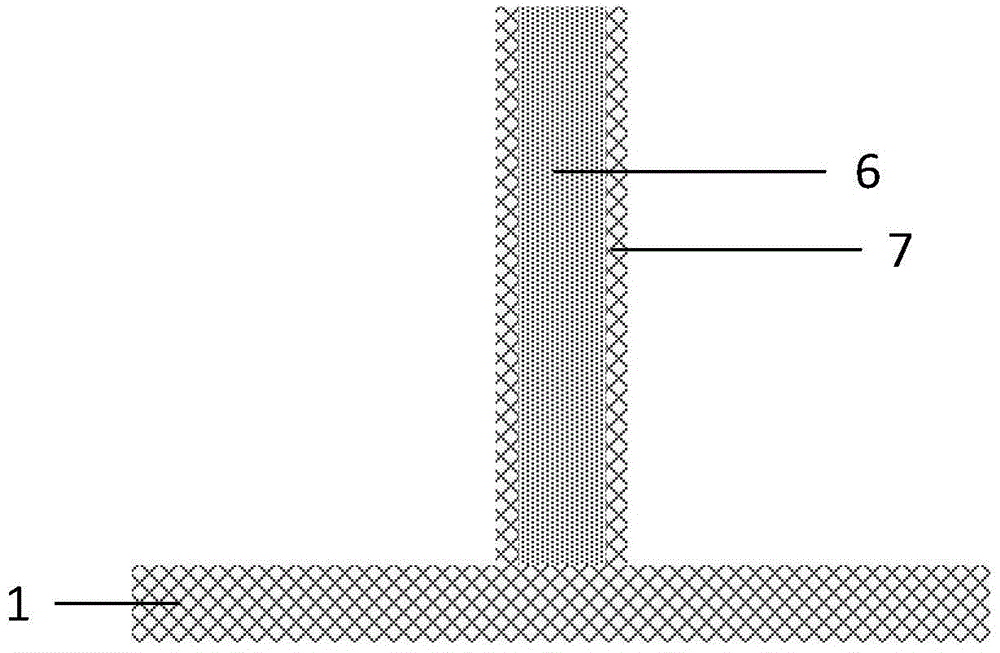

[0042]The present invention provides a gate-all-around field effect transistor combining a vertical channel, a core-shell structure and a junctionless structure, comprising a ring-shaped semiconductor core 6 in a vertical direction, a ring-shaped semiconductor shell 7 in a vertical direction, and a ring-shaped semiconductor shell 7 in a vertical direction. Gate electrode 9, a ring-shaped gate dielectric layer 8, a core source region 2, a core drain region 3, a shell source region 4, a shell drain region 5, and a semiconductor substrate 1; wherein, the core source region 2 is located vertically The bottom of the core channel 6 is connected to the substrate 1, the core drain region 3 is located on the top of the vertical core channel 6; the shell source region 4 is located at the bottom of the vertical shell channel 7, connected to the substrate 1, and the shell drain region 5 is located on the top of the vertical shell channel 7; the shell channel 7 surrounds the core channel 6 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More