Low-temperature polycrystalline silicon thin film manufacturing method, low-temperature polycrystalline silicon thin film and related devices

A technology of low-temperature polysilicon and a manufacturing method, which is applied to low-temperature polysilicon thin film transistors, array substrates and display devices, low-temperature polysilicon thin films and their manufacturing fields, can solve the problems affecting the performance of thin film transistors, threshold voltage drift, etc., and achieve uniform grain size. , The effect of preventing threshold voltage drift and uniform temperature

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to make the technical problems, technical solutions and advantages to be solved by the embodiments of the present invention clearer, the following will describe in detail with reference to the drawings and specific embodiments.

[0039] Embodiments of the present invention provide a low-temperature polysilicon thin film and a manufacturing method thereof, a low-temperature polysilicon thin-film transistor, an array substrate, and a display device, which can reduce alkali metal ions in the low-temperature polysilicon thin film, thereby effectively preventing threshold voltage drift of the low-temperature polysilicon thin-film transistor.

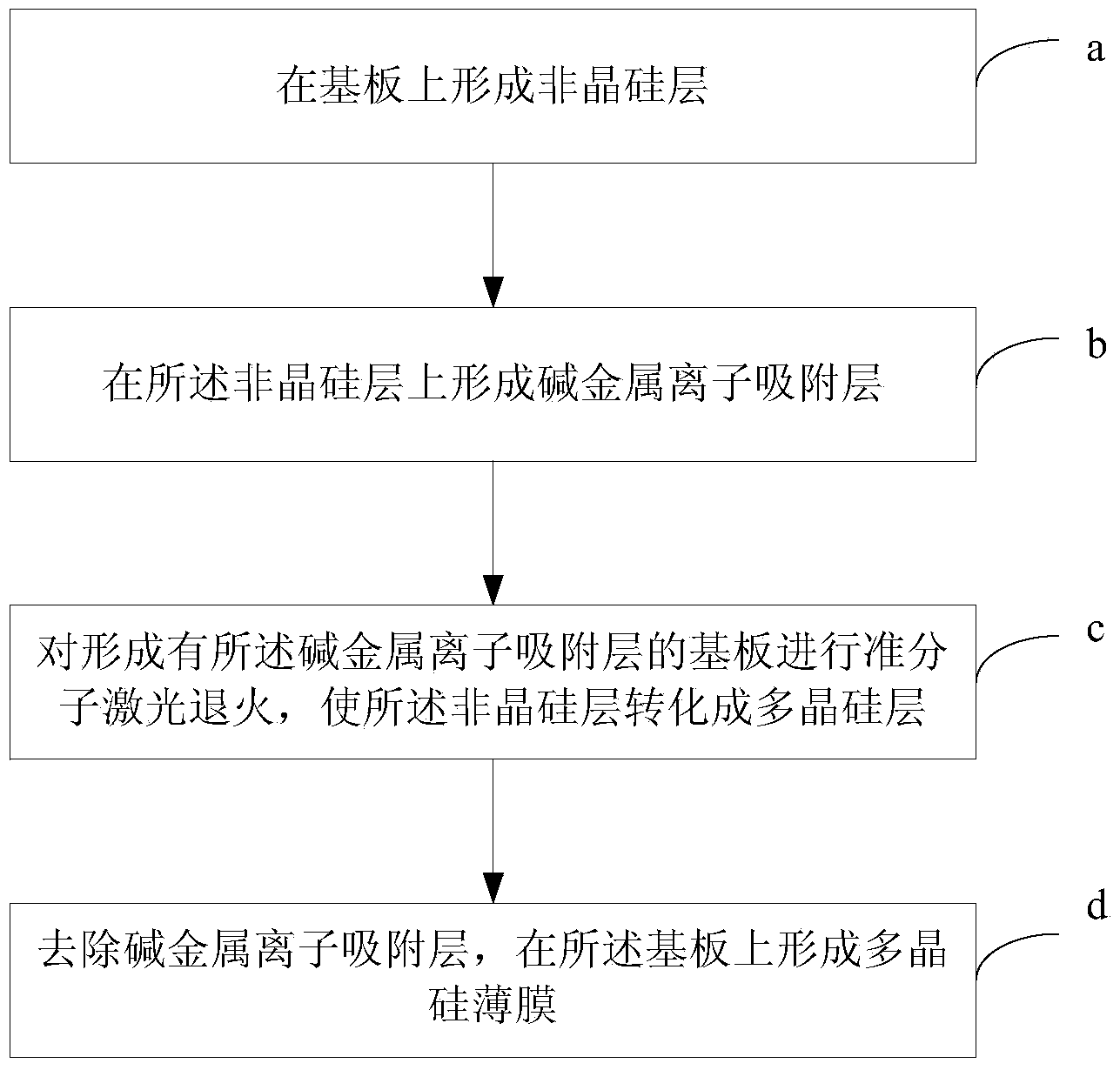

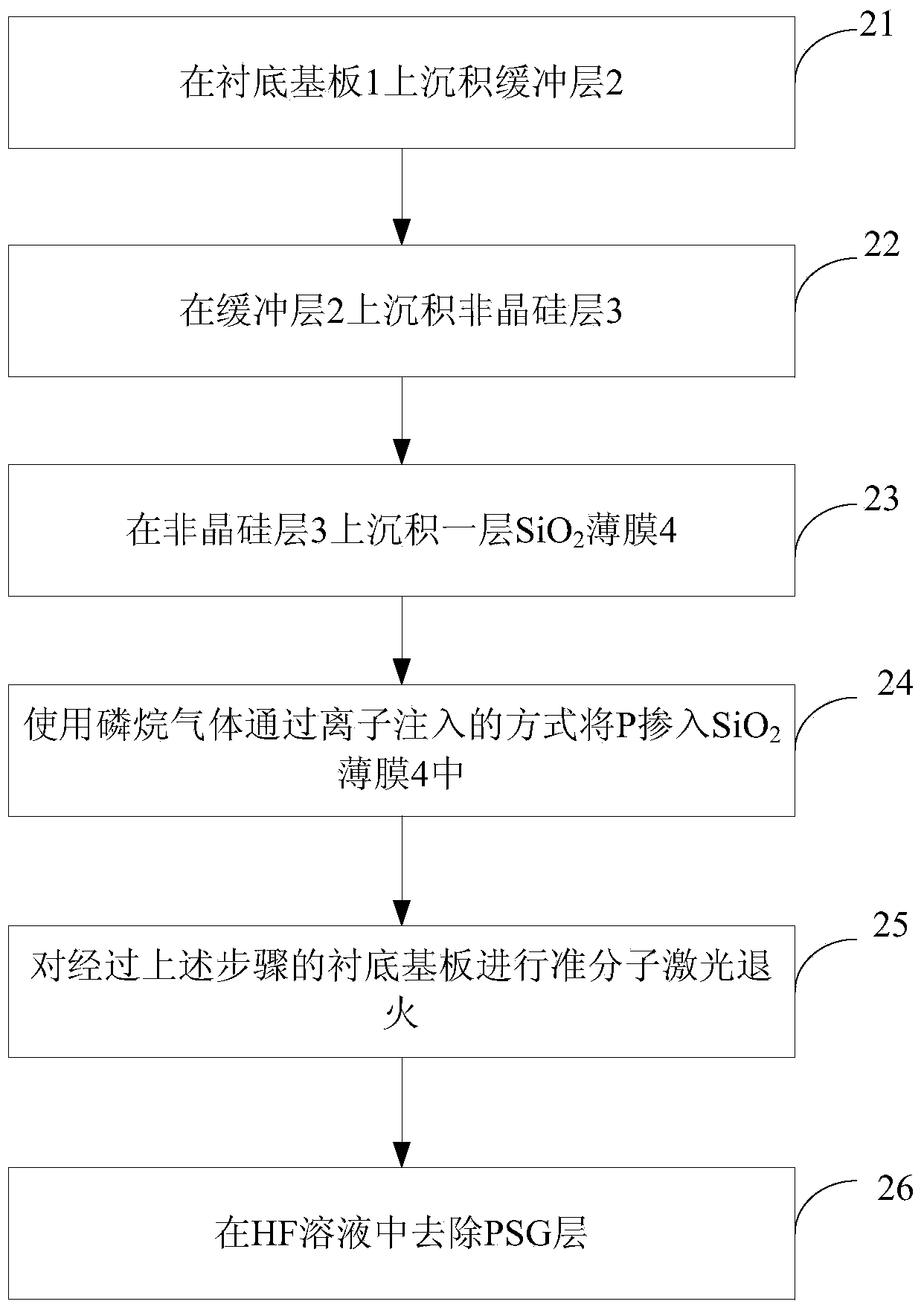

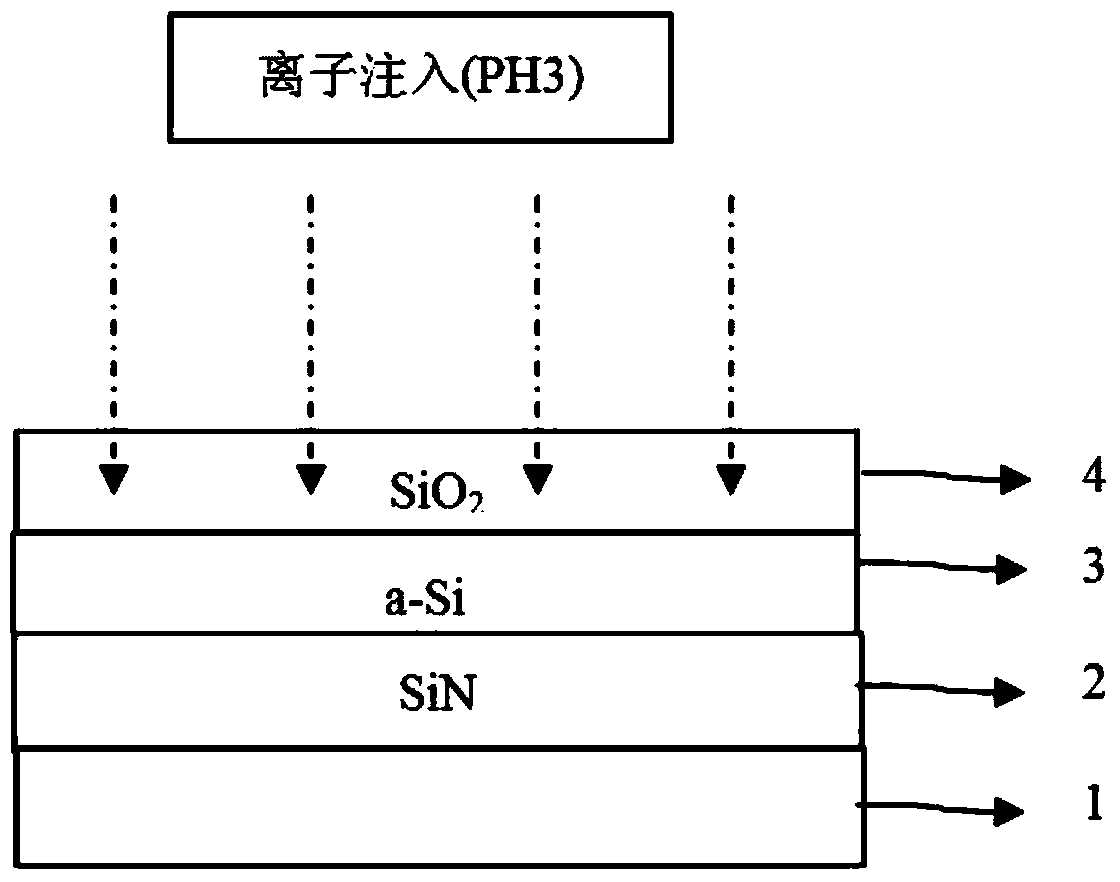

[0040] Embodiments of the present invention provide a method for manufacturing a low-temperature polysilicon film, such as figure 1 As shown, this embodiment includes:

[0041] Step a: forming an amorphous silicon layer on the substrate;

[0042] Step b: forming an alkali metal ion adsorption layer on the amorphous silicon la...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More