A circuit layout structure

A technology of circuit layout and dielectric layer, which is applied in the field of special circuit layout structure, can solve the problems of inability to connect electrically, inability to expose metal contact plugs, etc., and achieve the effect of reducing the capacitive effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

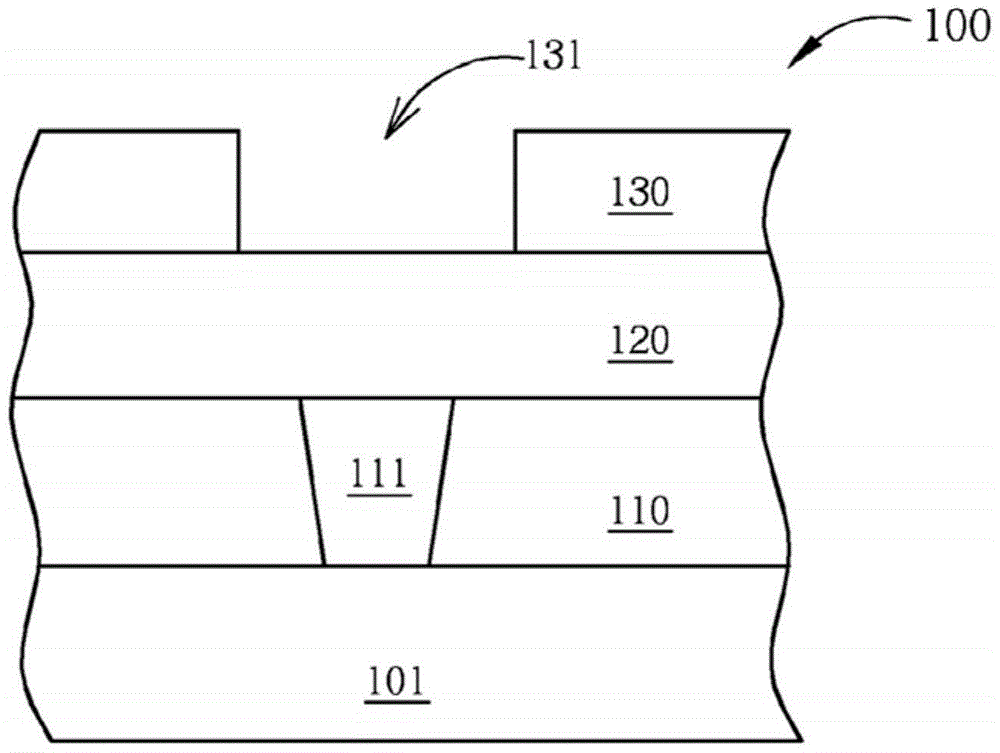

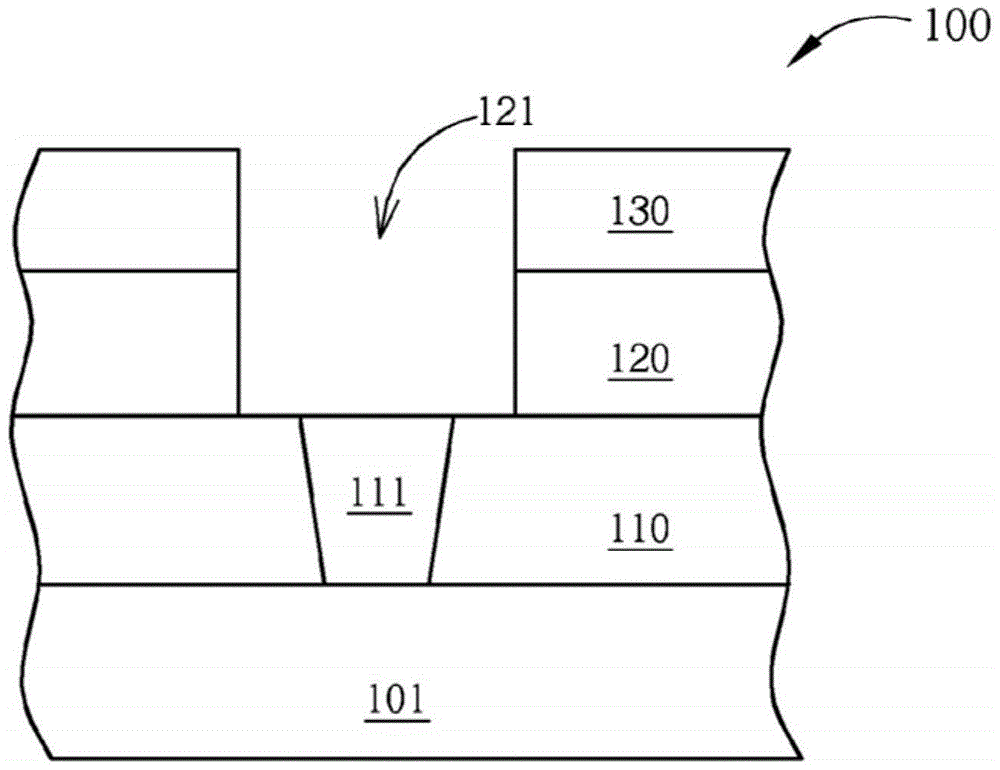

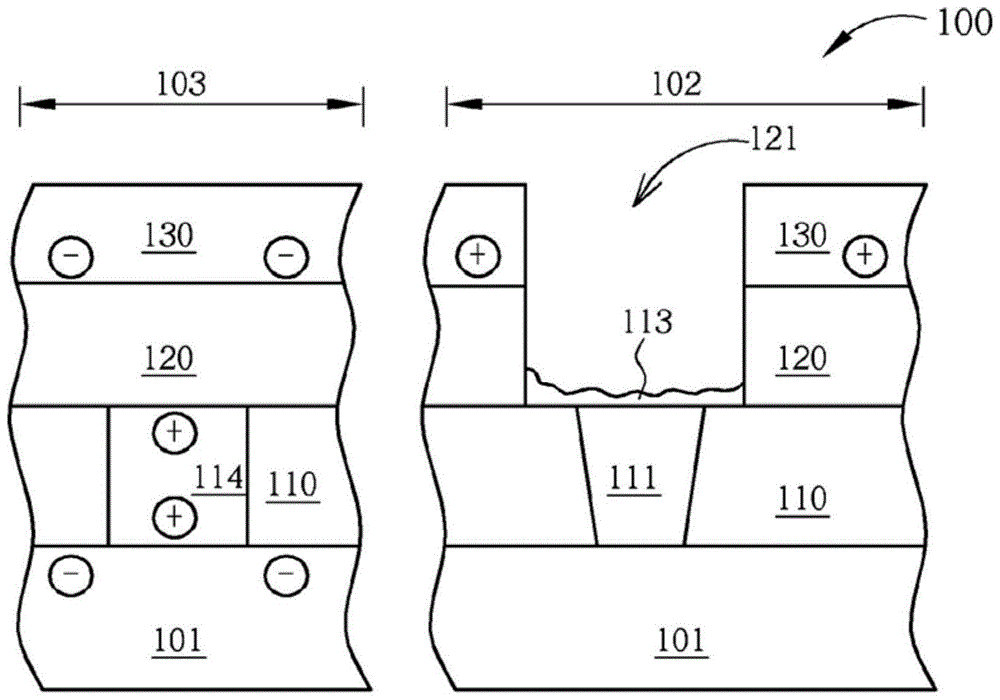

[0048] The present invention provides various novel circuit layout structures. In the circuit layout structure provided by the present invention, the metal mask and the metal pattern located in the scribe line can be properly isolated to reduce the charge induction between the metal mask and the metal pattern. Therefore, during the etching step, excessive etching residues are blocked in the trenches, hindering the etching process, and making it difficult to expose the underlying metal contact plugs. Especially when the metal mask is adjacent to the dicing line with the metal pattern, there will not be too much etching residue blocked in the groove of the inter-metal dielectric layer for the preparation of the metal interconnection, thus effectively avoiding the metal The problem that it is difficult to form an electrical connection between the interconnection wire and the underlying metal contact plug.

[0049] Figure 4A A cross-sectional view illustrating the first embodim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More