Non-volatile memory with low power consumption and low erase and write voltage based on standard technology

A non-volatile, low-power technology, applied in the field of microelectronics, can solve the problem of high power consumption, achieve the effect of reducing application cost, not easy to breakdown, and shortening the technology development cycle

Active Publication Date: 2018-04-03

NAT UNIV OF DEFENSE TECH

View PDF9 Cites 0 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

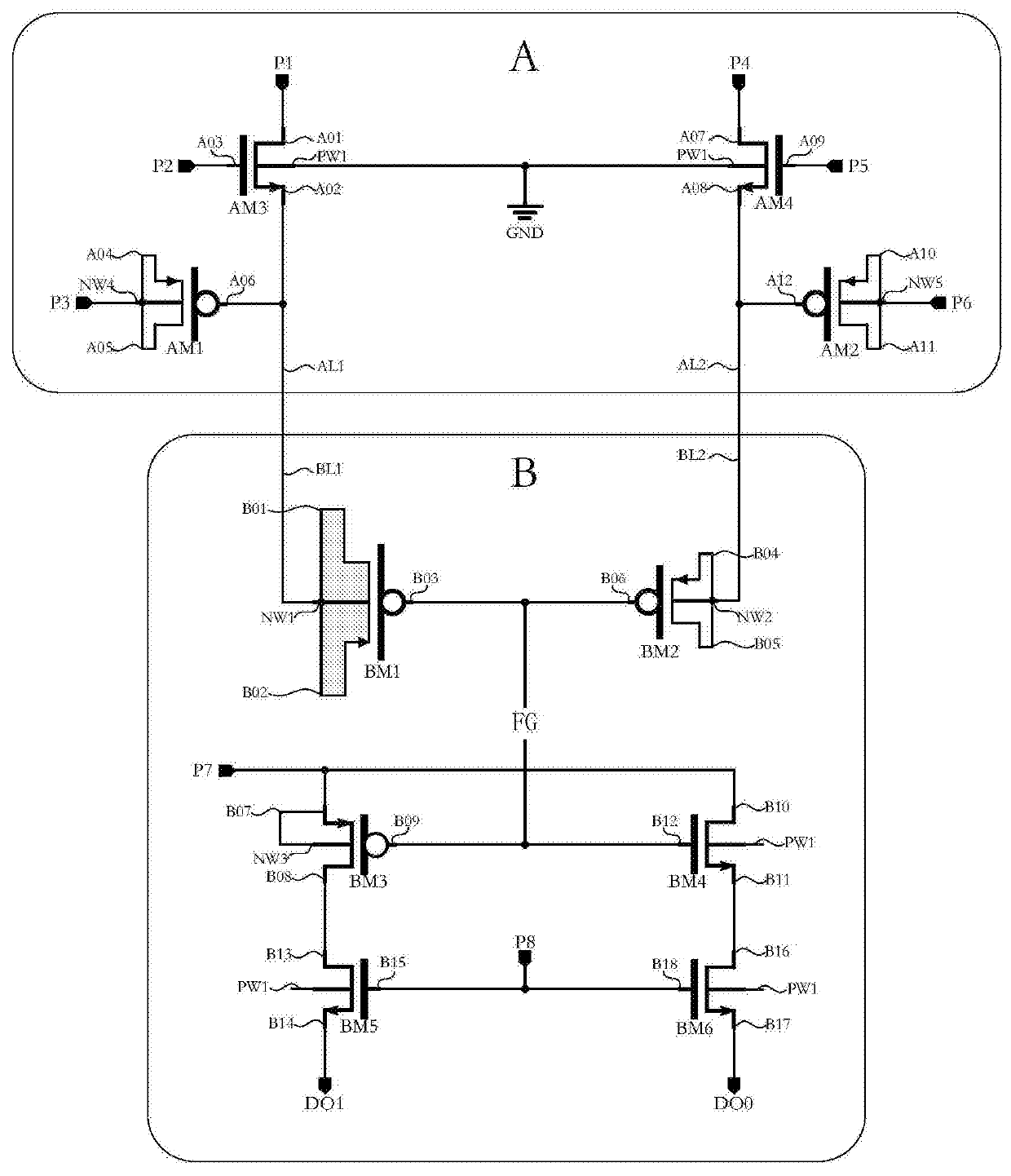

The purpose of the present invention is to provide a non-volatile memory with low power consumption and low erasing voltage based on standard technology to solve the above-mentioned deficiencies in the prior art. Its programming and erasing operations are all completed by using the FN tunneling effect. Solve the problem of high power consumption; use the pseudo-differential memory cell structure, output differential signals, high reliability, and help to use the differential structure of the sensitive amplifier to improve the read speed; the programming and erasing process requires only a low Voltage (about half of the normal high voltage) can be realized, so the high voltage generation circuit can be simplified

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

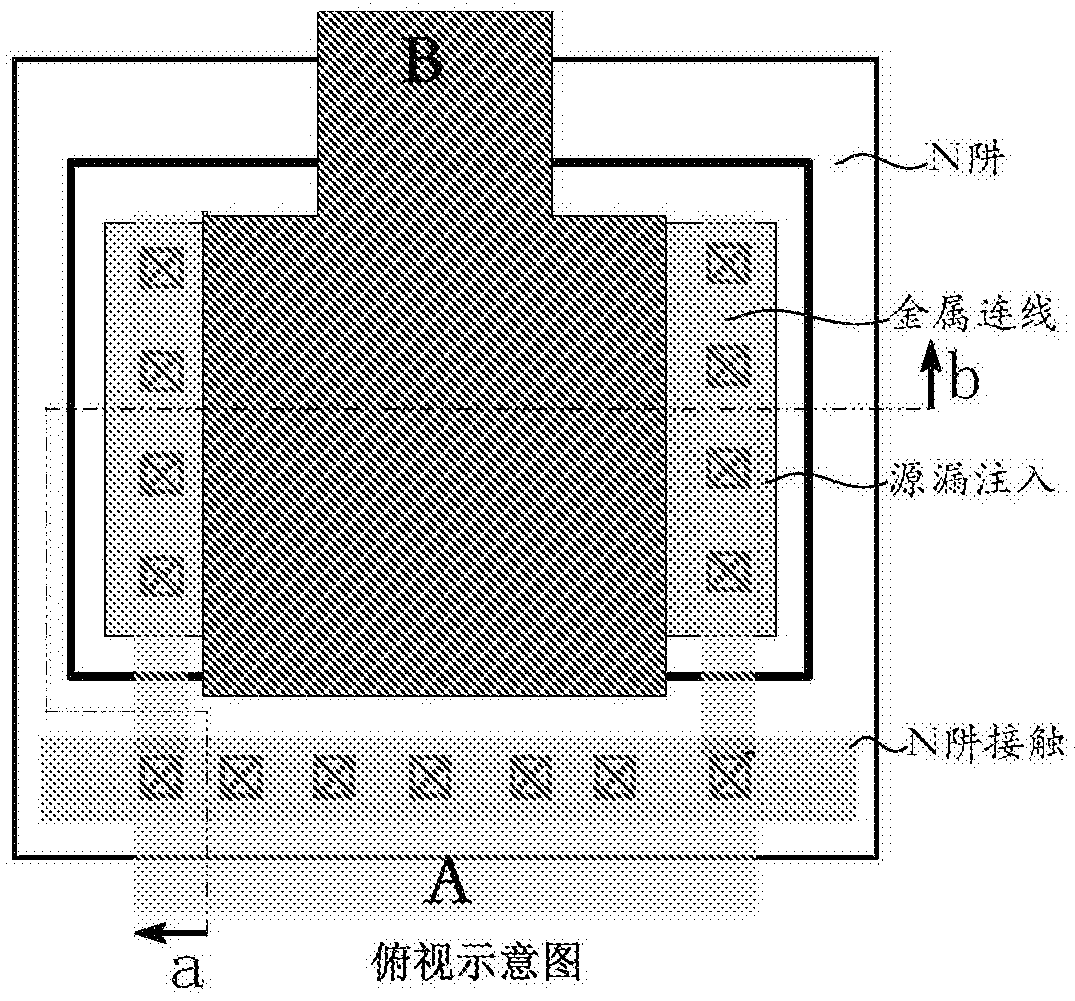

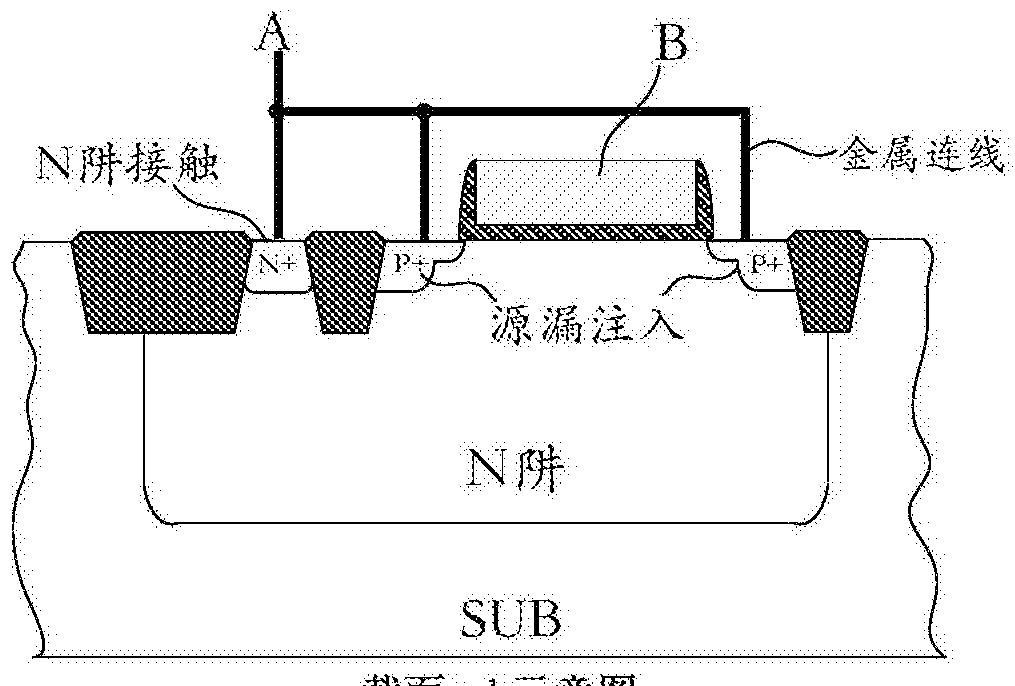

The invention discloses a non-volatile memory with low power consumption and low erasing and writing voltage based on standard technology. Its programming and erasing operations are all completed by FN tunneling effect, which solves the problem of high power consumption and reduces the area. Including multiple storage units, each storage unit is composed of module A and module B, module A is composed of four transistors: the first booster tube AM1, the second booster tube AM2, the first charging tube AM3, and the second charging tube AM4 . Module B consists of a control tube BM1, a tunnel tube BM2, a first read tube BM3, a second read tube BM4, a first selection tube BM5 and a second selection tube BM6. All transistors are of single polysilicon gate structure and gate oxide layer of the same thickness, and the storage unit is compatible with standard CMOS technology; the invention reduces application cost, shortens technology development period, has relatively fast reading speed and high reliability.

Description

Non-volatile memory with low power consumption and low erase / write voltage based on standard process technical field The invention belongs to the technical field of microelectronics, relates to a storage technology of a semiconductor integrated circuit, in particular to a nonvolatile memory with low power consumption and low erasing voltage based on a standard process. Background technique Many integrated electronic devices require some amount of non-volatile memory. Usually non-volatile memory is used as an independent memory outside the chip or as a memory in the tag chip, mainly to store some control programs, processing instructions or items related to the chip for a long time without power supply. information and more. Several types of non-volatile memory commonly used at present mainly include erasable programmable read-only memory EPROM, electrically erasable programmable read-only memory EEPROM and flash memory Flash Memory. In addition, there are ferroelectric ...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Patents(China)

IPC IPC(8): G11C16/10G11C16/14

Inventor 李建成李文晓李聪尚靖王震吴建飞王宏义谷晓忱李松亭

Owner NAT UNIV OF DEFENSE TECH