Low-temperature polycrystalline silicon thin-film transistor based on dual-gate structure and preparation method thereof

A technology of thin-film transistors and low-temperature polysilicon, applied in the direction of transistors, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve problems such as channel light leakage, and achieve the effects of enhanced charging capacity, small size, and increased pixel aperture ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

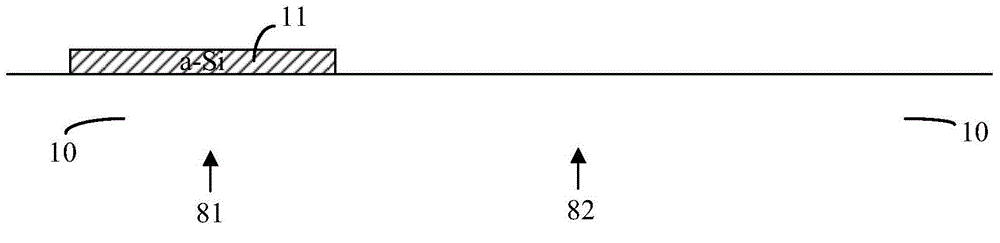

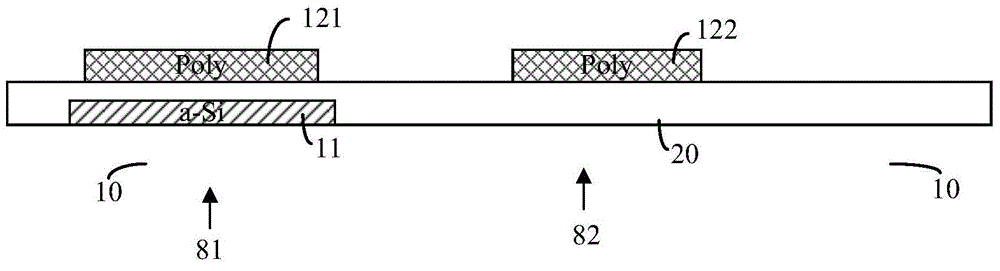

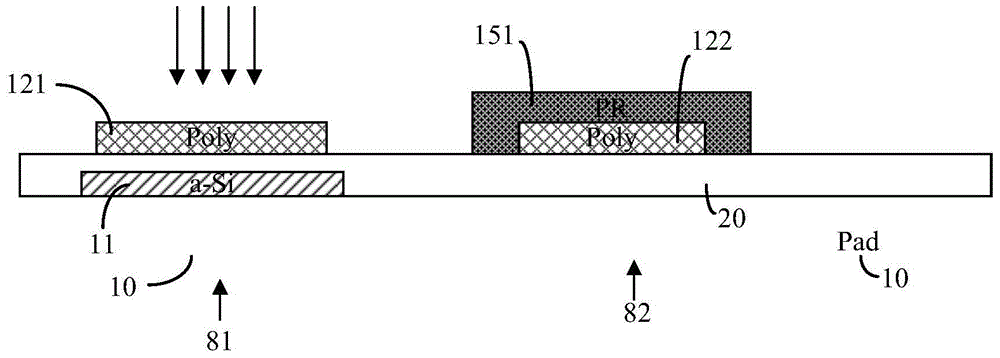

[0025] The description of the following embodiments refers to the attached drawings to illustrate specific embodiments that the present invention can be implemented.

[0026] For an embodiment of the present invention, please refer to Picture 9 , Is a low-temperature polysilicon thin film transistor based on a double-gate structure, including: a substrate 10, at least one patterned amorphous silicon layer 11 (Amorphous silicon, a-si), an N-type metal oxide semiconductor 81 (NMOS), And a P-type metal oxide semiconductor 82 (PMOS). The at least one patterned amorphous silicon layer 11 (Amorphous silicon, a-si) is located in a barrier layer 20 (barrier layer) on the substrate 10, and the at least one patterned amorphous silicon layer 11 forms a Bottom gate; the N-type metal oxide semiconductor 81 is located on the barrier layer 20; and the P-type metal oxide semiconductor 82 is located on the barrier layer 20; wherein, the N The metal oxide semiconductor 81 has a patterned gate e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More