Semiconductor device and method for forming semiconductor device

A semiconductor and device technology, applied in the field of semiconductor manufacturing, can solve the problems of increasing the difficulty of shallow trench isolation structure filling process, and achieve the effects of avoiding breakdown or leakage, improving electrical properties, and small width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

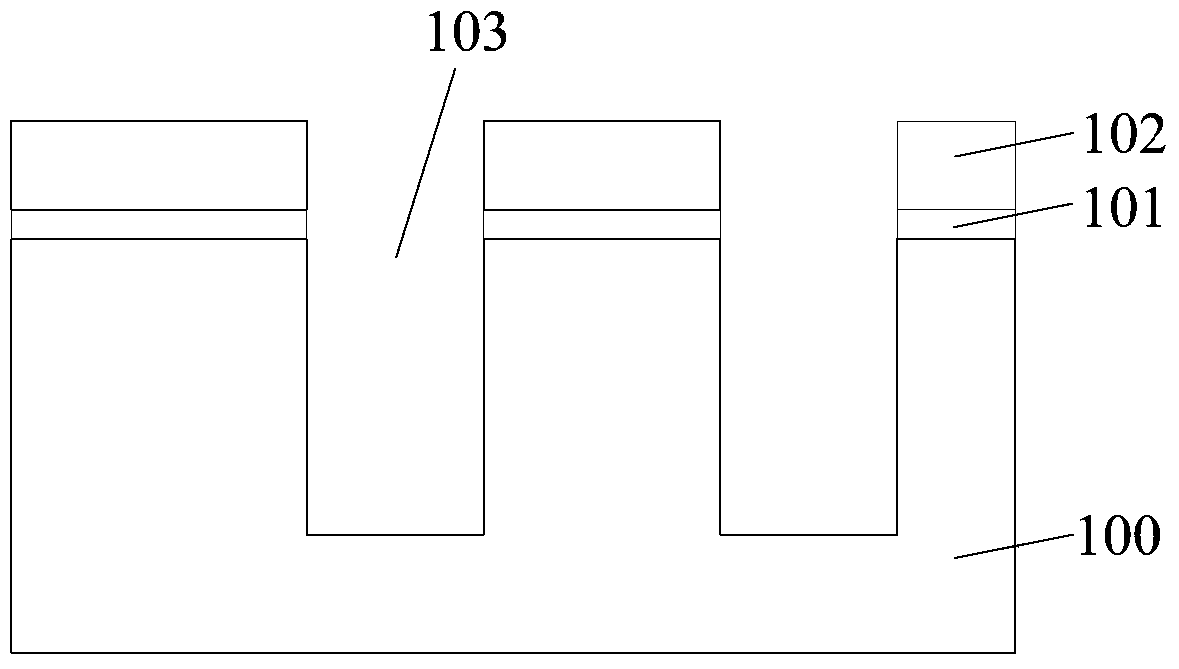

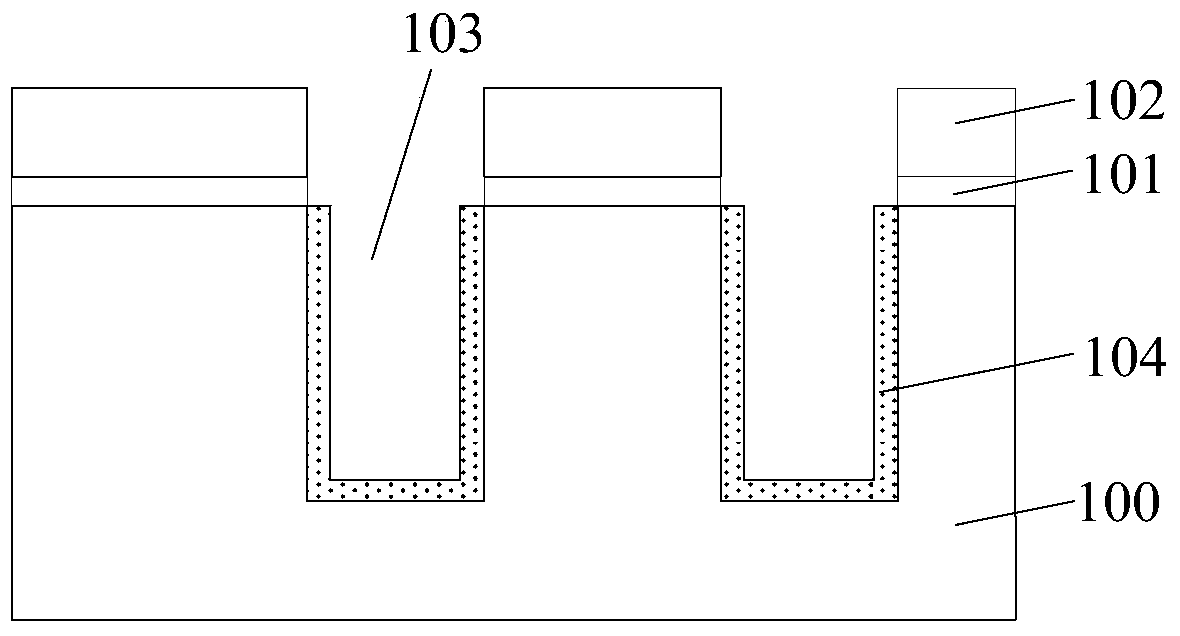

[0049] Figure 6 to Figure 12 It is a schematic cross-sectional structure diagram of the formation process of the semiconductor device according to the first embodiment of the present invention.

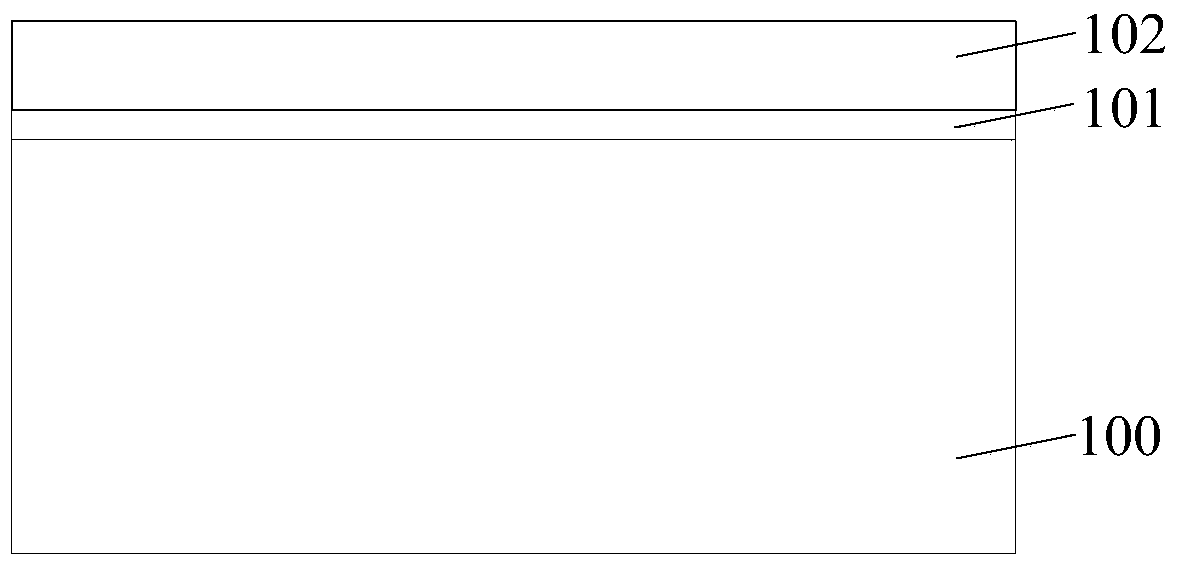

[0050] Please refer to Figure 6 1. A semiconductor substrate 200 is provided. A pad oxide layer 201 and a hard mask layer 202 on the surface of the pad oxide layer 201 are formed on the surface of the semiconductor substrate 200 .

[0051] The semiconductor substrate 200 is used to provide a platform for subsequent processes.

[0052] The semiconductor substrate 200 is one of single crystal silicon, polycrystalline silicon, amorphous silicon or silicon-on-insulator; the semiconductor substrate 200 can also be a Si substrate, a Ge substrate, a GeSi substrate or a GaAs substrate .

[0053] In this embodiment, the semiconductor substrate 200 is a silicon substrate.

[0054] Active areas (AA: Active Areas) are defined in the semiconductor substrate 200 by a doping process such as an...

no. 2 example

[0118] In the first embodiment, after the epitaxial layer 204 is formed, the hard mask layer 202 and the pad oxide layer 201 are removed. Since the first isolation layer 203 in the shallow trench isolation structure is relatively thin, the first isolation layer 203 will be Etching by the etching process in the subsequent semiconductor device formation process may cause adverse effects.

[0119] In order to avoid the above adverse effects, the present invention also provides a more optimized method for forming a semiconductor device.

[0120] The difference between the second embodiment and the first embodiment is that, before removing the hard mask layer and the pad oxide layer after forming the epitaxial layer, a step is further included: forming a second isolation dielectric layer filling the second trench, The top of the second isolation dielectric layer is flush with the surface of the hard mask layer.

[0121] It should be noted that the formation of the epitaxial layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More