n-type ldmos device and process method

A device, N-type technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as unfavorable breakdown voltage, achieve the effect of improving potential distribution, uniform electric field distribution, and increasing breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

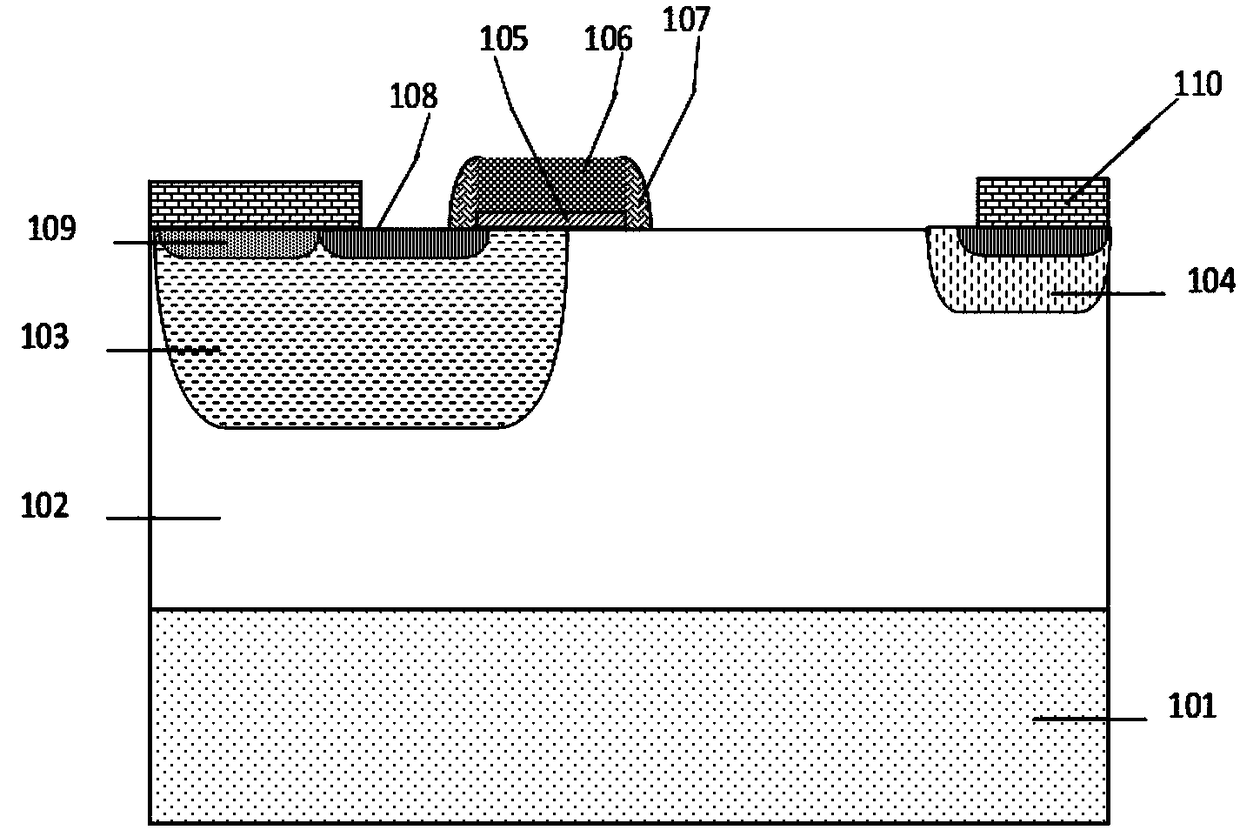

[0023] The N-type LDMOS device described in the present invention, such as Figure 8 As shown, there are P wells 103 and N wells 104 in the N-type deep wells 102 on the P-type substrate 101, and the substrate surface has polysilicon gates 106 and sidewall structures 107; there are LDMOS devices in the N wells 104 Drain region 111, there is a metal electrode 110 on the drain region 111 to lead the drain region 111; the P well 103 has a source region 108 of an LDMOS device, and a heavily doped P-type region 109, and the metal electrode will heavily dope the P-type region 109 and the source region 108 are drawn; the surface of the LDMOS device is a non-planar stepped structure, the position of the drain region is higher than the channel of the LDMOS, and the height difference h on both sides is

[0024] In order to solve the above problems, the process method of the N-type LDMOS device of the present invention comprises the following process steps:

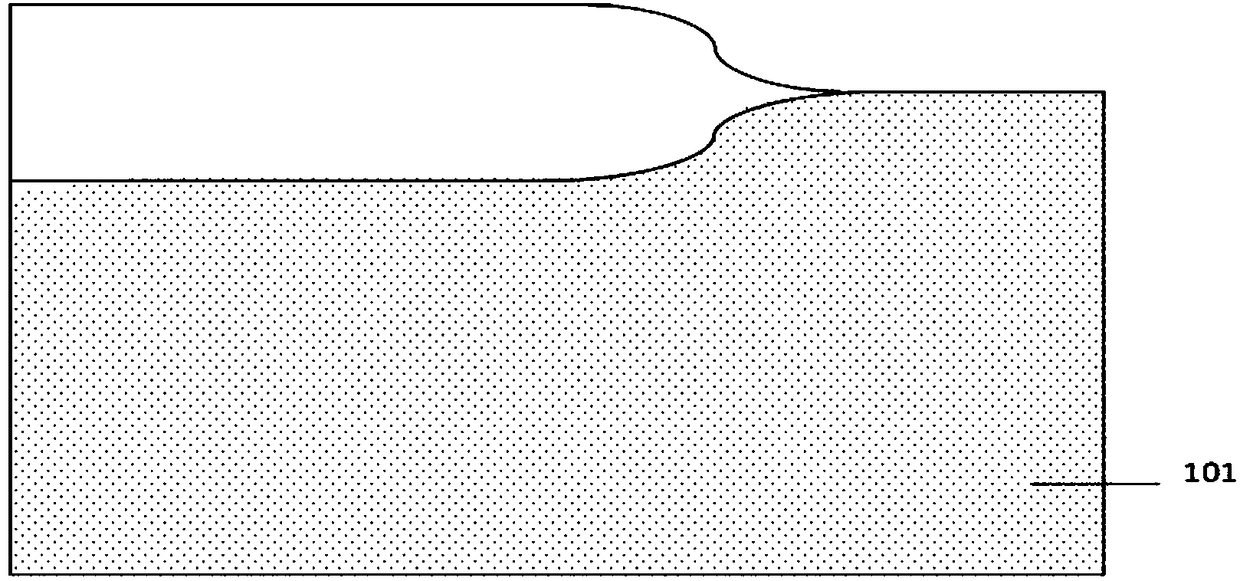

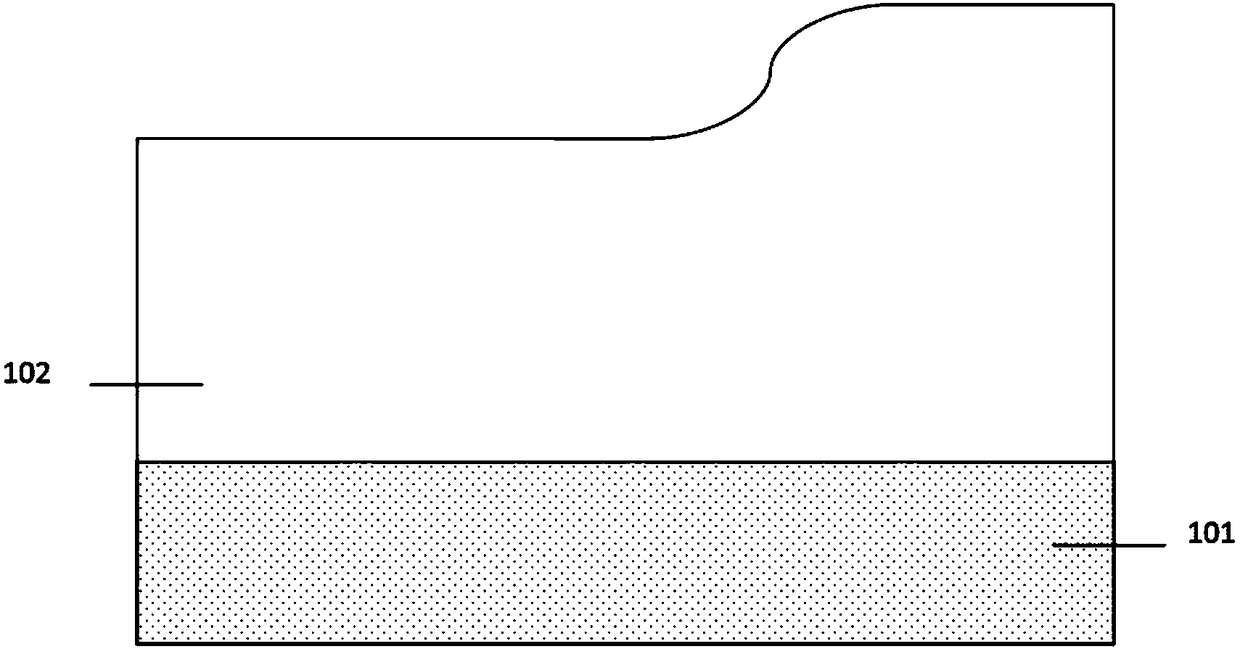

[0025] Step 1, on the P-ty...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More