Rapidio controller using window mapping mechanism and its control method

A technology of mapping mechanism and control method, applied in the direction of instrumentation, electrical digital data processing, etc., can solve problems that cannot be solved by processors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

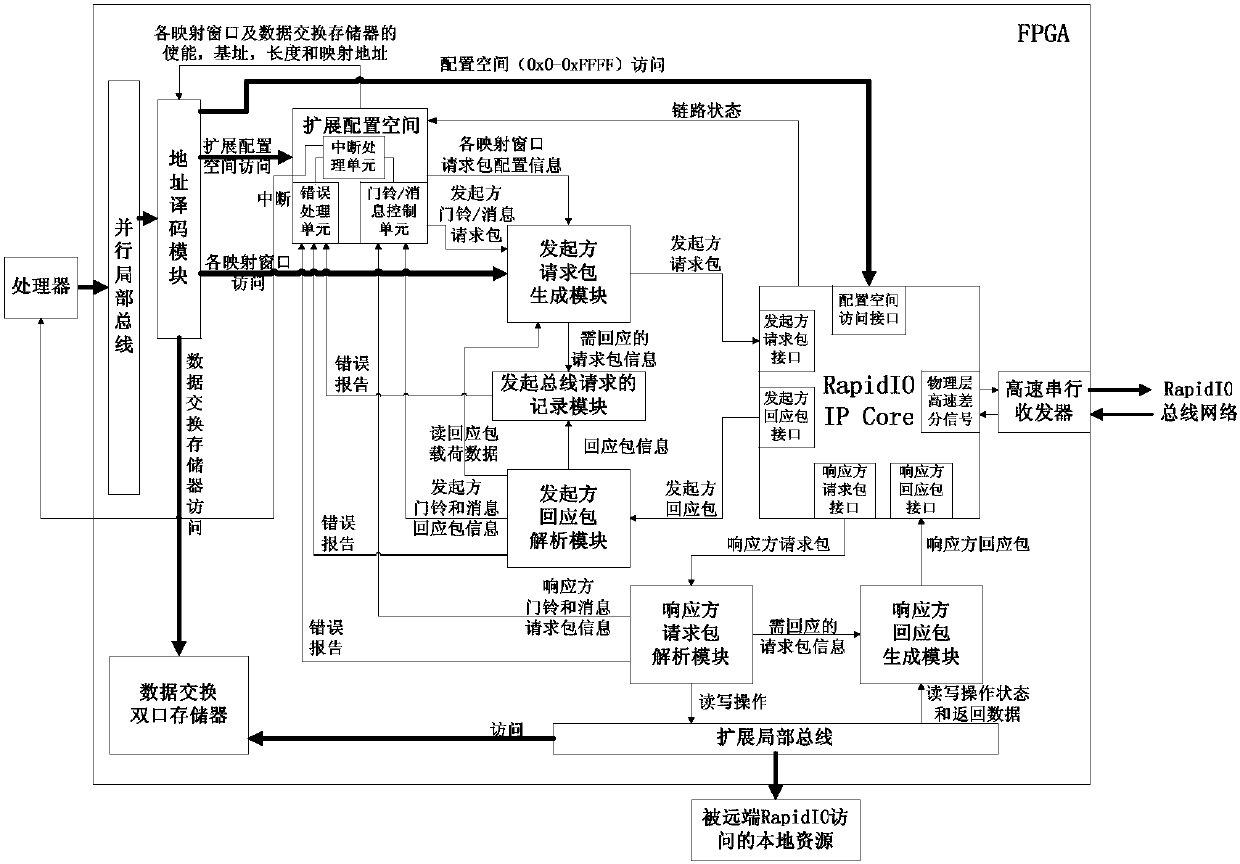

[0067] This controller is realized by using FPGA with high-speed serial transceiver as the platform and carrying out secondary development on the basis of conventional RapidIO programmable logic IP Core. The front end of the controller is a parallel local bus, and the back end is The high-speed serial interface of the RapidIO interface adopts the mechanism of address window mapping to realize the mutual conversion between the parallel local bus operation and the RapidIO bus operation.

[0068] The hardware composition of this controller is as attachedfigure 1 shown. The controller is obtained through secondary development on the conventional RapidIO programmable logic IPCore, attached figure 1 The square module in the middle on the right is the RapidIO IP Core, which realizes the mutual conversion between the high-speed serial code on the physical link and the parallel data signal in the RapidIO packet format. RapidIO IPCore mainly has six external interfaces, namely "configu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More