Universal pulse width modulation method for multi-level inverter

A multi-level inverter, pulse width modulation technology, applied in the direction of AC motor control, control system, electrical components, etc., can solve problems such as electromagnetic interference, common mode voltage and common mode current interference, capacitor voltage imbalance, etc. Achieve the effect of improving safety and work performance, strong feasibility and effectiveness, good scalability and portability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be further described in detail below in conjunction with the drawings.

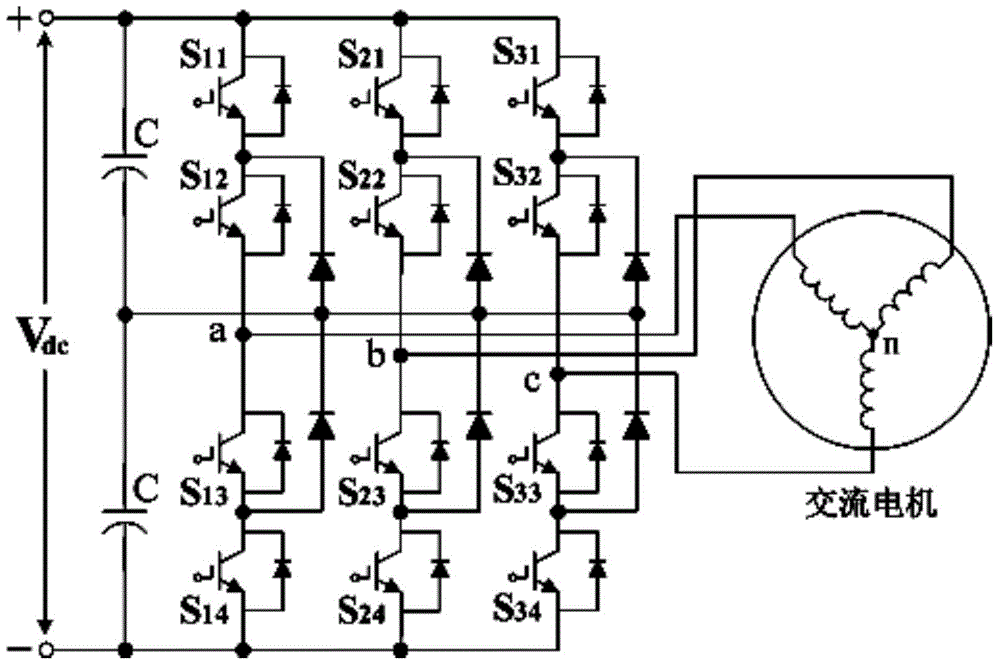

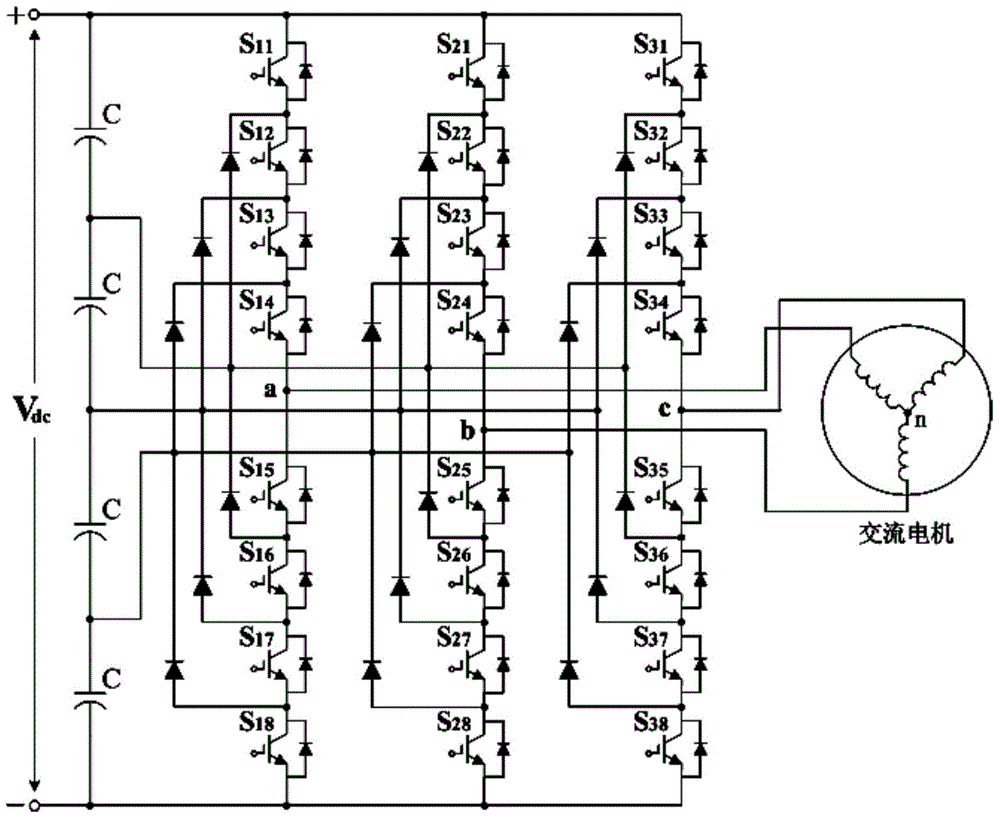

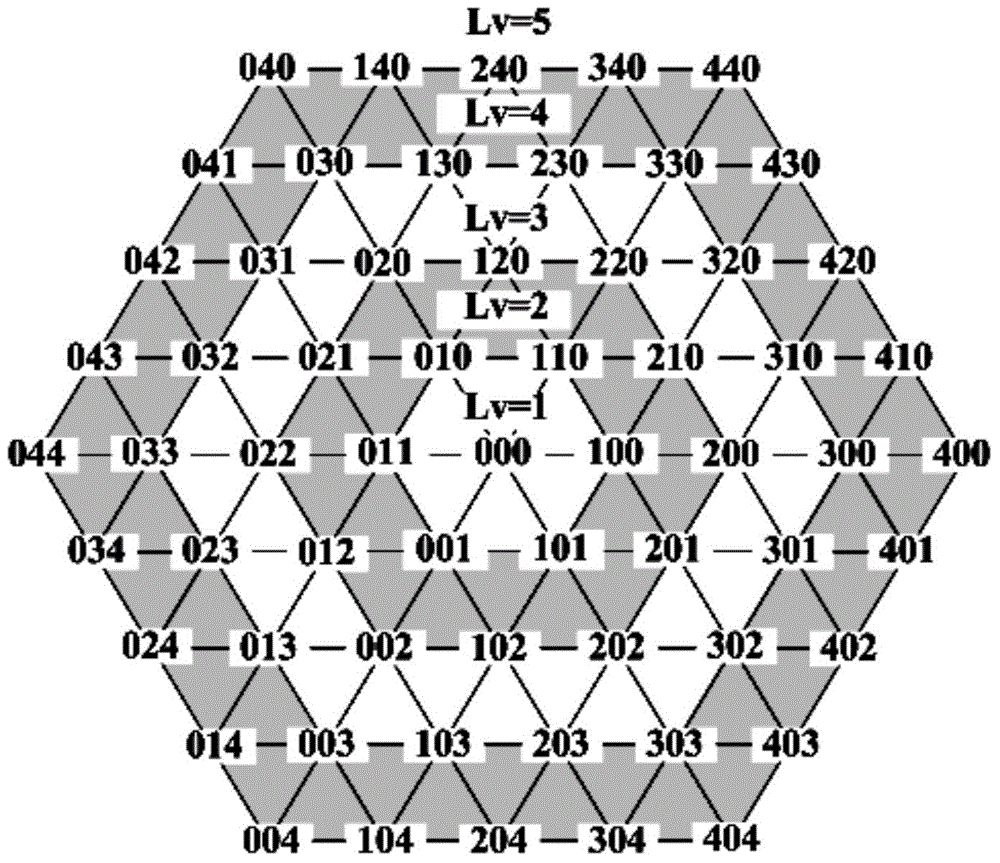

[0044] See figure 1 , 2, For odd-numbered multi-level inverters, such as three-level inverters, five-level inverters, seven-level inverters, etc., if the traditional space vector modulation method is used to achieve the synthesis of reference voltage vectors , The implemented algorithm is more complicated, and the conventional algorithm will cause the inverter output voltage to contain common mode voltage components, which greatly affects the inverter output performance. The present invention proposes a pulse width modulation technology that can effectively suppress common mode voltage components. Taking the traditional five-level inverter topology as an example, the inverter consists of three power switch bridge arms, a DC bus power supply and four It is composed of a voltage divider capacitor, and each bridge arm is composed of eight power switches and six clamping diodes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More