Chip manufacture process and chip

A manufacturing process and chip technology, which is applied in the chip manufacturing process and the field of chips, can solve the problems of easy short circuit of chips and poor quality of finished products, and achieve the effects of high manufacturing reliability, stable connection, guaranteed quality of finished products and reliability of use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The embodiments of the application will be described in detail below with reference to the accompanying drawings, but the application can be implemented in many different ways defined and covered by the claims.

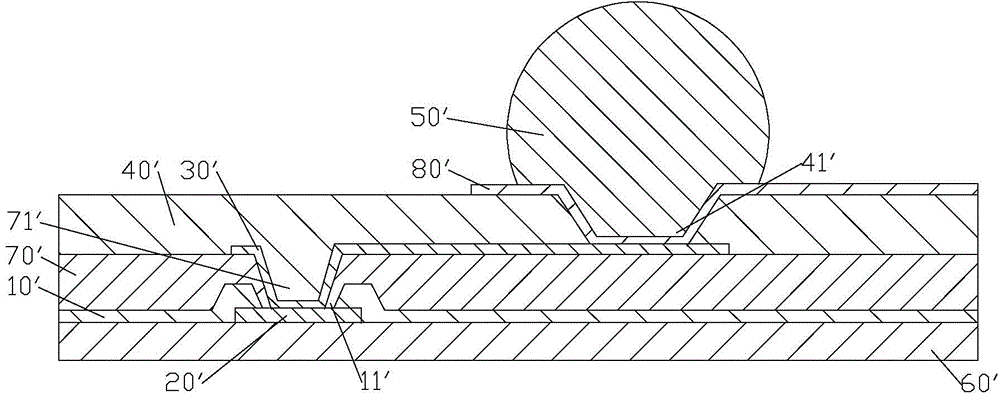

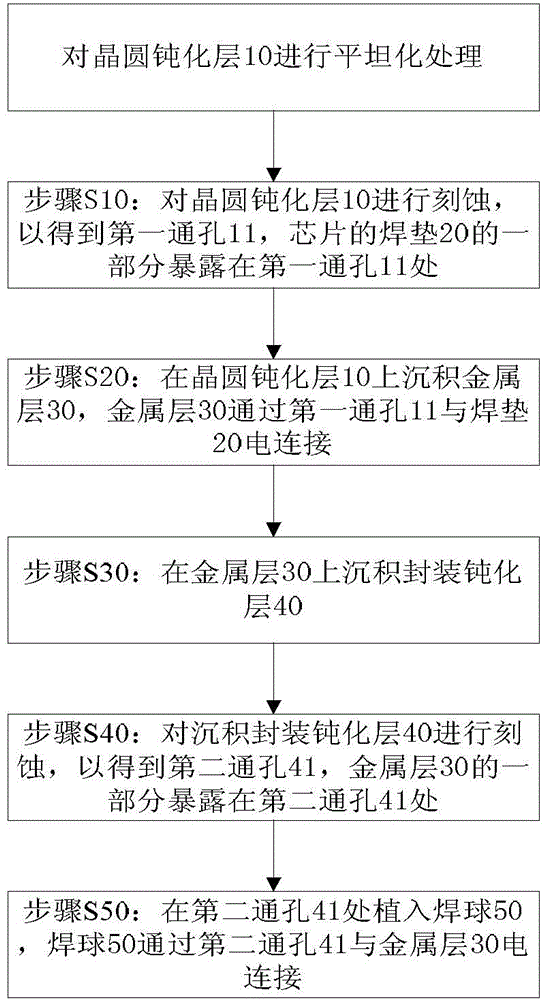

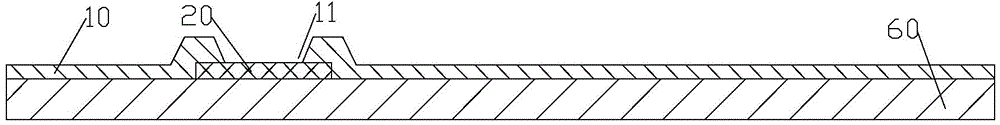

[0029] In order to solve the problems pointed out in the background art that chips are prone to short circuits and poor quality of finished products, the present application provides a chip manufacturing process. Such as Figure 2 to Figure 7 As shown, the chip manufacturing process includes planarizing the wafer passivation layer 10 . After the wafer passivation layer 10 is planarized, the surface of the wafer passivation layer 10 is flatter, the uneven feeling is reduced, and the fine grooves are eliminated, thus making the metal layer deposited on the wafer passivation layer 10 30 and the wafer passivation layer 10 are connected more firmly and evenly, thereby avoiding the loosening of the metal layer 30, and solving the problem that the metal layer 30 exte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More