On-chip integrated transformer

A technology that integrates transformers and transformers. It is applied in the direction of transformers/inductor coils/windings/connections, electric solid-state devices, semiconductor devices, etc., and can solve the problems of transformer performance circuit stability, crosstalk shielding, and system reliability problems. and other problems, to achieve the effect of increasing production cost, low loss, and reducing chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

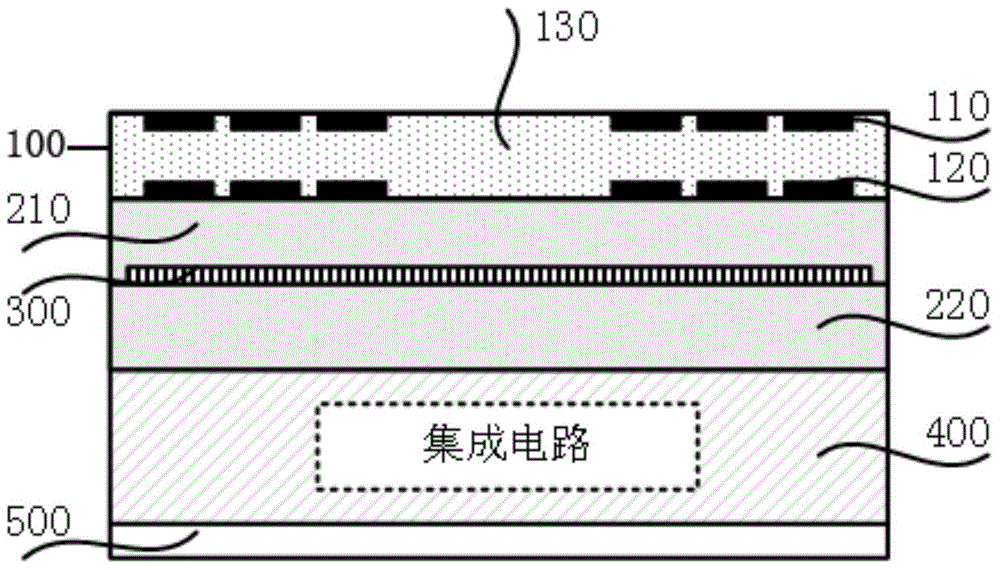

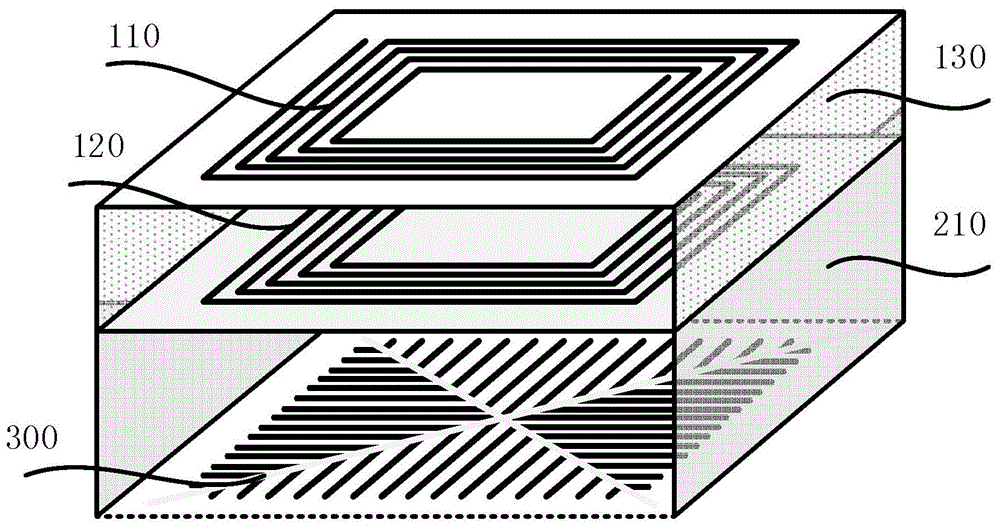

[0017] The invention provides an on-chip integrated transformer, which includes a circuit layer and a transformer layer stacked on the circuit layer, and also includes a shielding layer stacked between the transformer layer and the circuit layer for shielding the electric field formed on the transformer layer. The invention makes the system highly single-chip integrated through the layered design, and can shield the interlayer crosstalk on the transformer layer by adding the shielding layer, so as to ensure the signal and power transmission performance of the transformer layer.

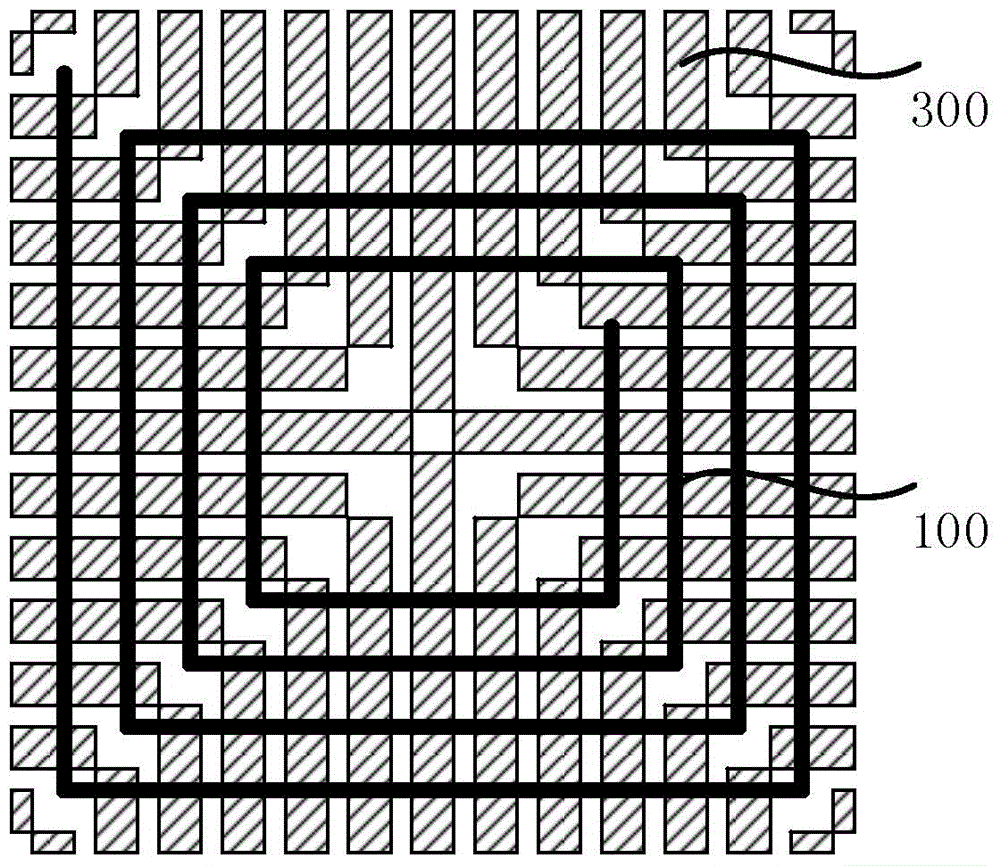

[0018] According to an embodiment of the present invention, the transformer layer may be a transformer on a silicon substrate, including a primary coil, an isolation layer and a secondary coil, the isolation layer is located between the primary coil and the secondary coil, and the primary Coils and secondary coils are formed by helically wound metal wires. The primary coil and the secondary coil trans...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More