Method for forming fin field effect transistor

A fin-type field effect and transistor technology, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems such as the performance of stress source/drain region needs to be improved, so as to reduce the generation of defects, enhance the activity, and ensure the growth environment Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] As mentioned in the background art, the performance of forming stress source / drain regions in the fins of the prior art fin field effect transistors still needs to be improved. For example, the formed stress source / drain regions have lattice defects and poor uniformity.

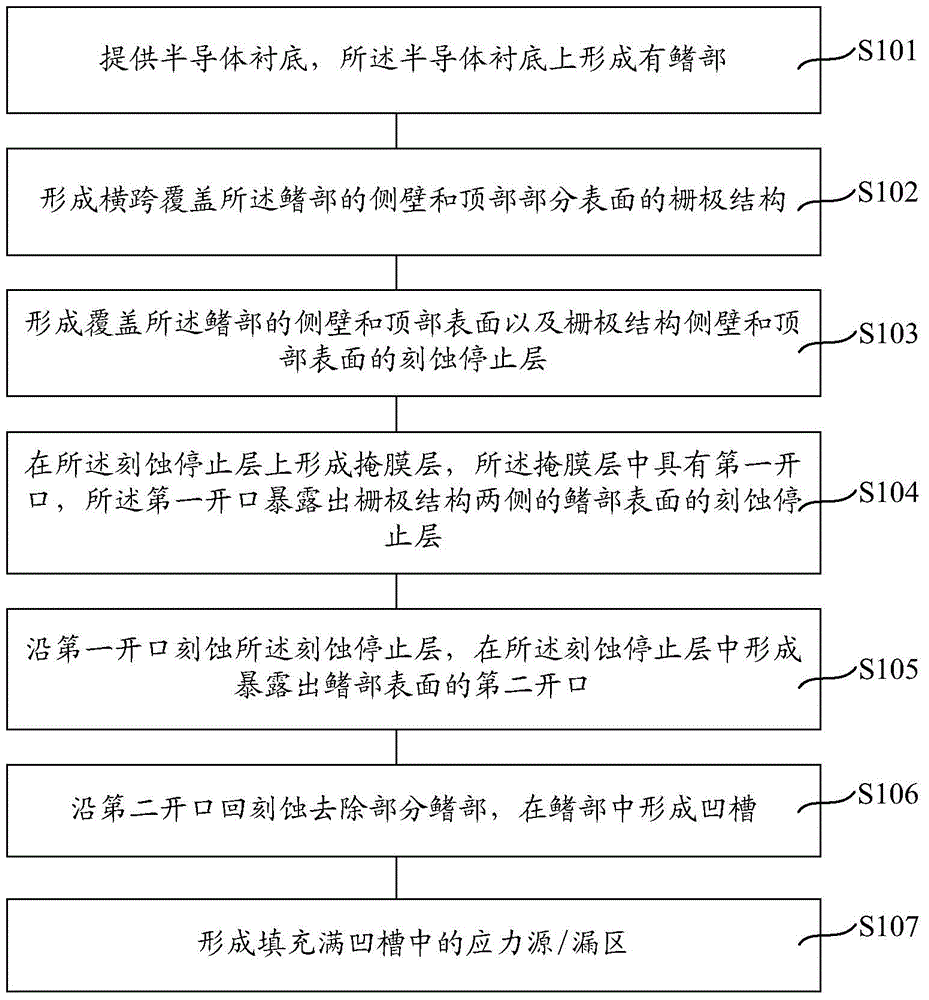

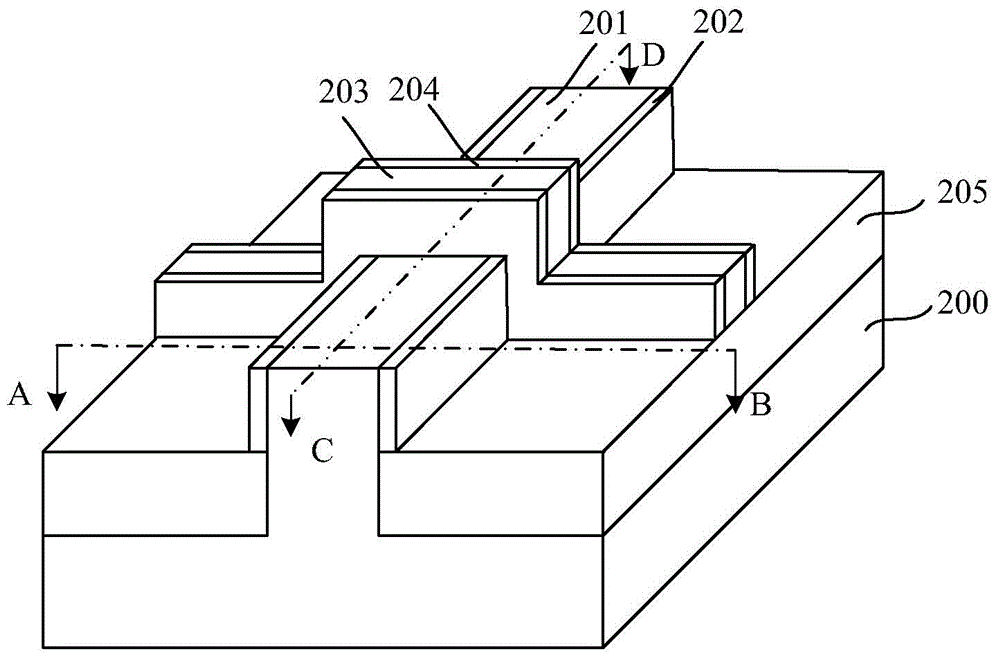

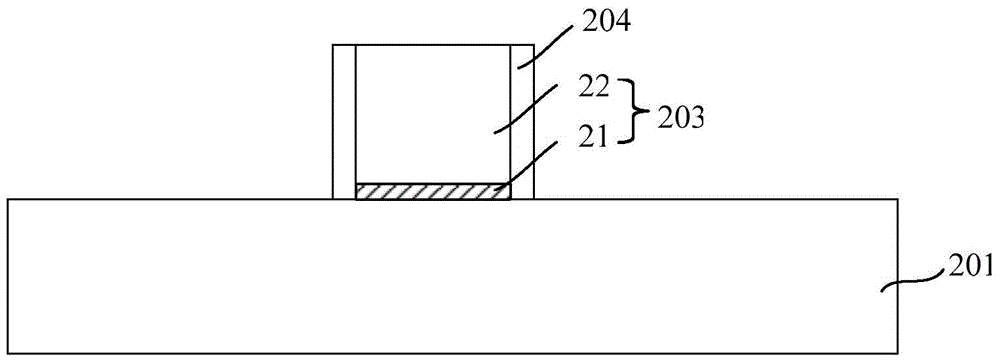

[0035] To study the formation process of fin field effect transistors, refer to figure 1 , Including the steps: step S101, providing a semiconductor substrate with a fin formed on the semiconductor substrate; step S102, forming a gate structure that spans the sidewall and top surface of the fin; step S103, forming Cover the sidewall and top surface of the fin and the etch stop layer on the sidewall and top surface of the gate structure; step S104, a mask layer is formed on the etch stop layer, the mask layer has a first An opening, the first opening exposes the etch stop layer on the surface of the fin on both sides of the gate structure; step S105, the etch stop layer is etched along the first opening, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More