Back-contact heterojunction solar cell and preparation method thereof

A solar cell and heterojunction technology, applied in circuits, photovoltaic power generation, electrical components, etc., can solve the problems of easy conduction, lower battery conversion efficiency, lower open circuit voltage and short circuit current, etc., achieve good repeatability, prevent leakage Current, the effect of increasing the open circuit voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

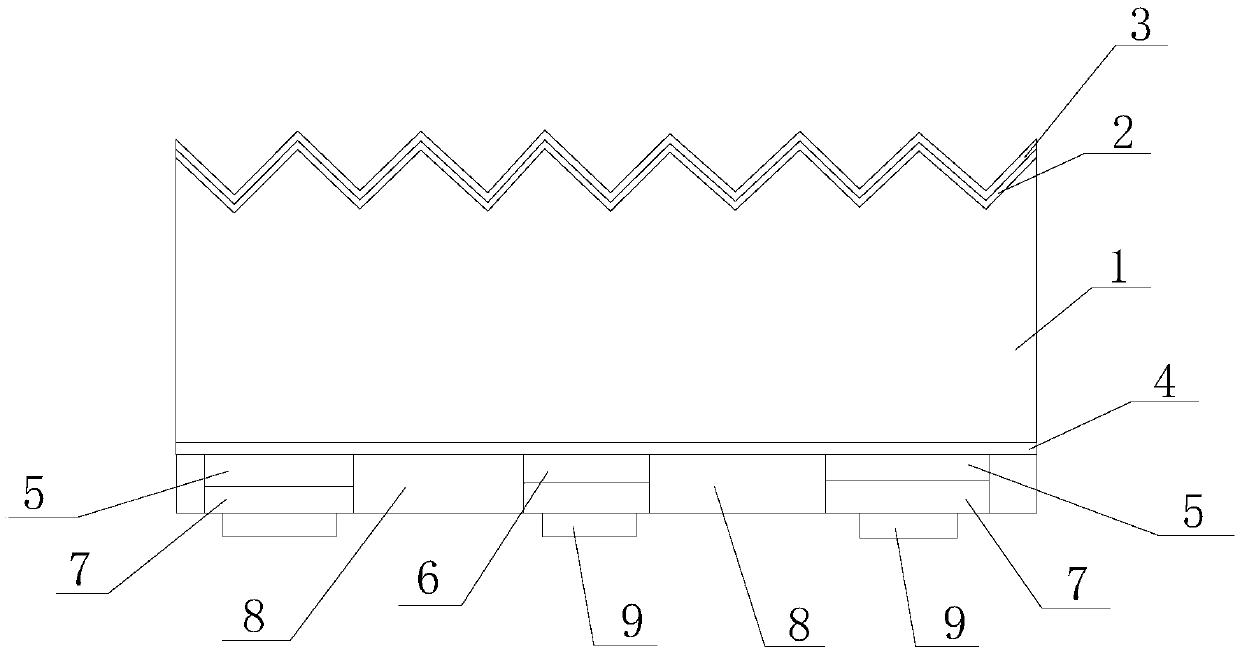

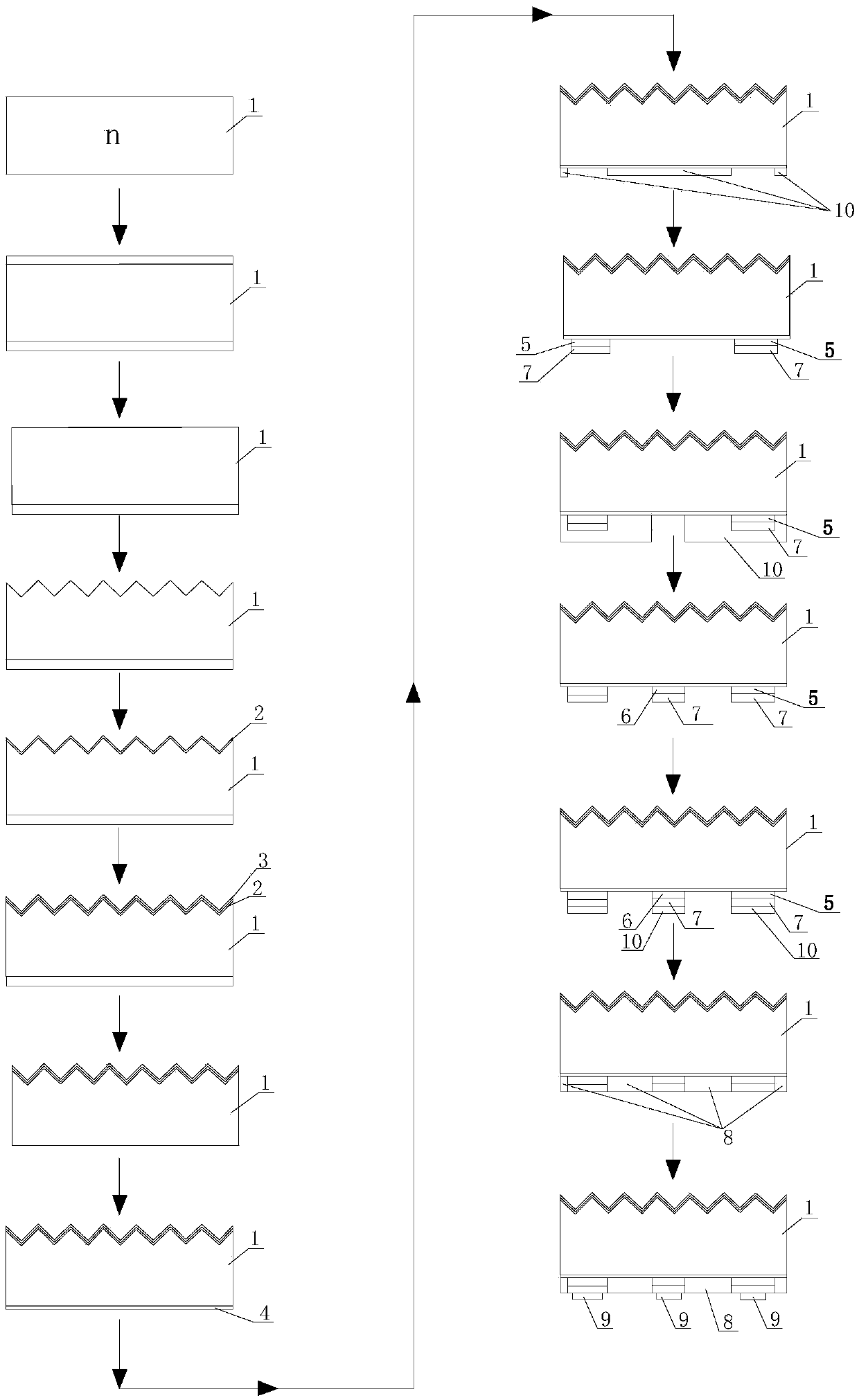

[0033] Such as figure 1 As shown, the full-back heterojunction solar cell of the present invention includes a silicon base layer 1, which is sequentially arranged on the front surface of the silicon base layer 1 N type The front surface field 2 and the antireflection layer 3 are provided with an intrinsic amorphous silicon passivation layer 4 on the back surface of the silicon base layer 1, and a P-type amorphous silicon layer is arranged at intervals on the intrinsic amorphous silicon passivation layer 4 5 and the N-type amorphous silicon layer 6, the P-type amorphous silicon layer 5 and the N-type amorphous silicon layer 6 are respectively provided with a transparent conductive film layer 7, and the transparent conductive film layer 7 is provided with an electrode. The thickness of the crystalline silicon layer 5 is 5-20nm, and the width is 100-1000μm; the thickness of the N-type amorphous silicon layer 6 is 5-20nm, and the width is 100-1000μm; The distance between the cen...

Embodiment 2

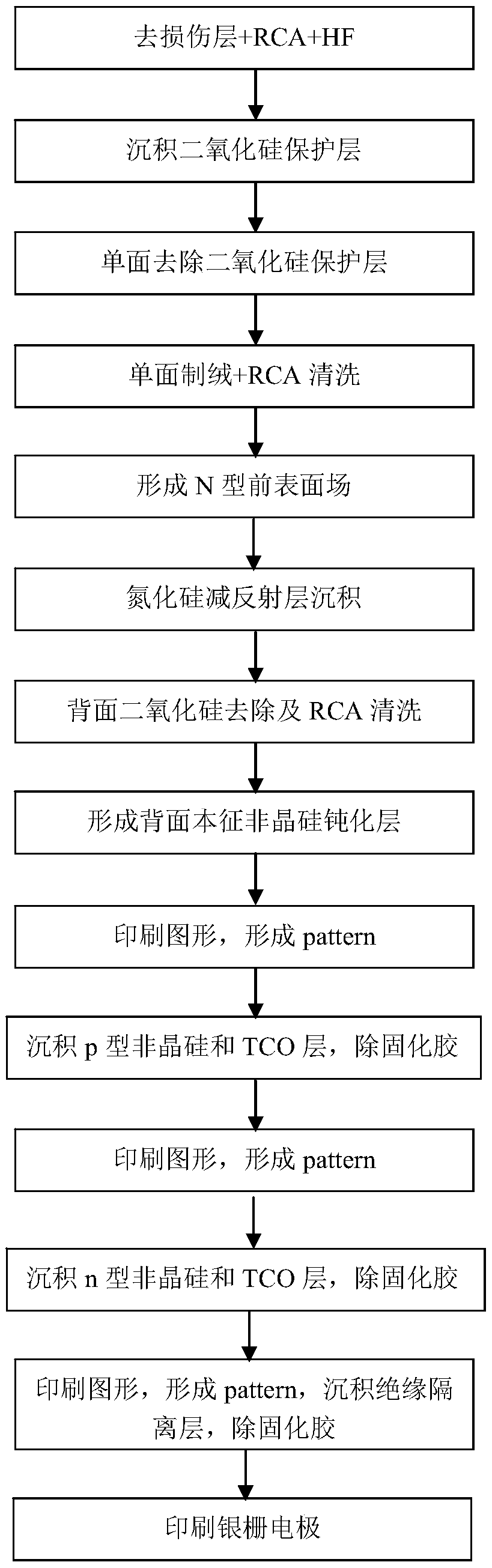

[0035] Such as figure 2 , image 3 As shown, taking the n-type silicon substrate as an example, the preparation method of the back contact heterojunction solar cell of the present invention comprises the following steps:

[0036] S1: providing a silicon wafer as the silicon base layer 1;

[0037] S2: Carry out standard RCA cleaning on the silicon base layer 1, and then use HF treatment to form a clean surface, rinse with deionized water and then blow dry;

[0038] S3: placing the silicon base layer 1 into a diffusion furnace, forming a silicon dioxide protective layer on the surface of the silicon base layer to protect the surface of the silicon wafer;

[0039] S4: Remove the silicon dioxide protective layer on one side, and form a pyramid structure on the front surface of the silicon substrate layer 1 through a single-side texturing process, followed by standard RCA cleaning;

[0040] S5: forming an N-type front surface field FSF2 on the pyramid structure through a diffus...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More