Integrated circuit packaging structure and packaging technology based on Flip-chip connection

An integrated circuit and packaging process technology, applied in the field of integrated circuit packaging structure and packaging process, can solve the problems of high cost, unguaranteed packaging reliability, long production cycle, etc. short cycle effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

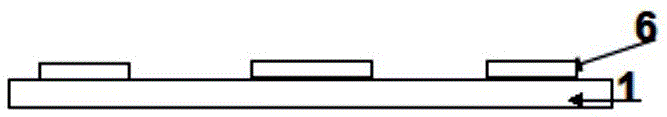

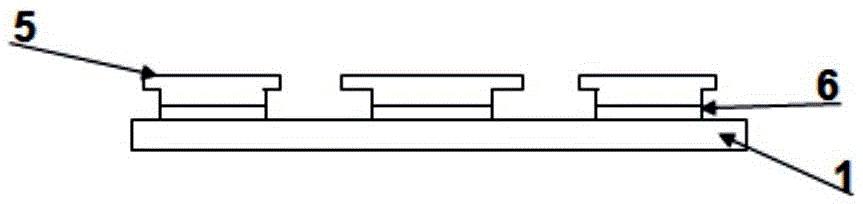

[0026] like Figure 9 As shown, a film-free and electroplating-free package based on Flip-chip connection, the package is mainly composed of metal bumps 2, chips 3, plastic package 4, chamfered silver-plated layer 5, and NiPdAu-plated layer 6 The chamfered silver-plated layer is a mutually independent silver-plated layer section, and metal bumps are planted on the chip, and the plastic package surrounds the metal bump, chip, NiPdAu-plated layer and chamfered silver-plated layer, and the metal Bumps, chips, chamfered silver-plated layers and NiPdAu-plated layers constitute the power and signal channels of the circuit.

[0027] The main process flow of a film-free and electroplating-free package based on Flip-chip connection: plating NiPdAu on the frame → growing a chamfered silver plating layer (through corrosion, the silver plating layer on the NiPdAu plating layer is formed as attached image 3 The chamfered groove shown) → wafer thinning → dicing → metal bumps on the chip →...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More