Interconnection structure of low-cost chip back through silicon via (TSV) and preparation method thereof

An interconnection structure and through-silicon via technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, electrical components, etc., can solve the problem of high cost, achieve low cost, reduce process cost, and reduce difficulty.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] In order to make the present invention more comprehensible, the specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings. For convenience of description, the components in the structures in the drawings of the embodiments are not scaled according to the normal scale, so they do not represent the actual relative sizes of the structures in the embodiments.

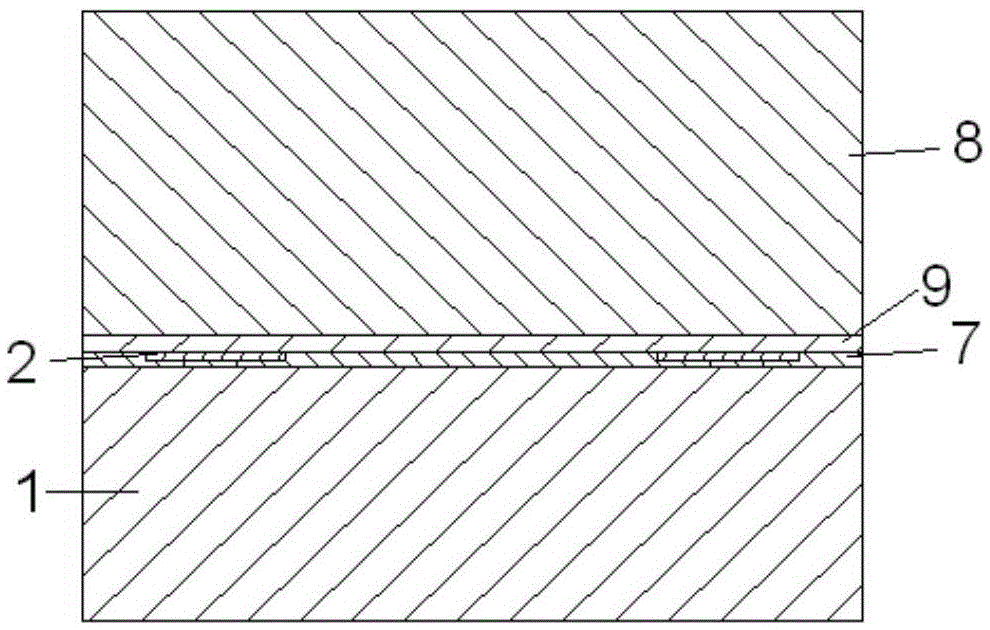

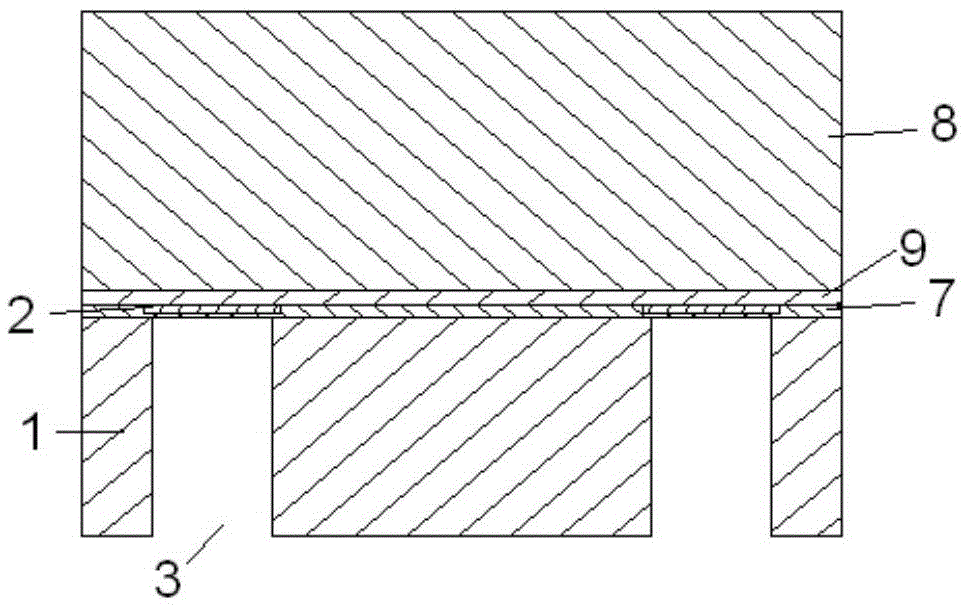

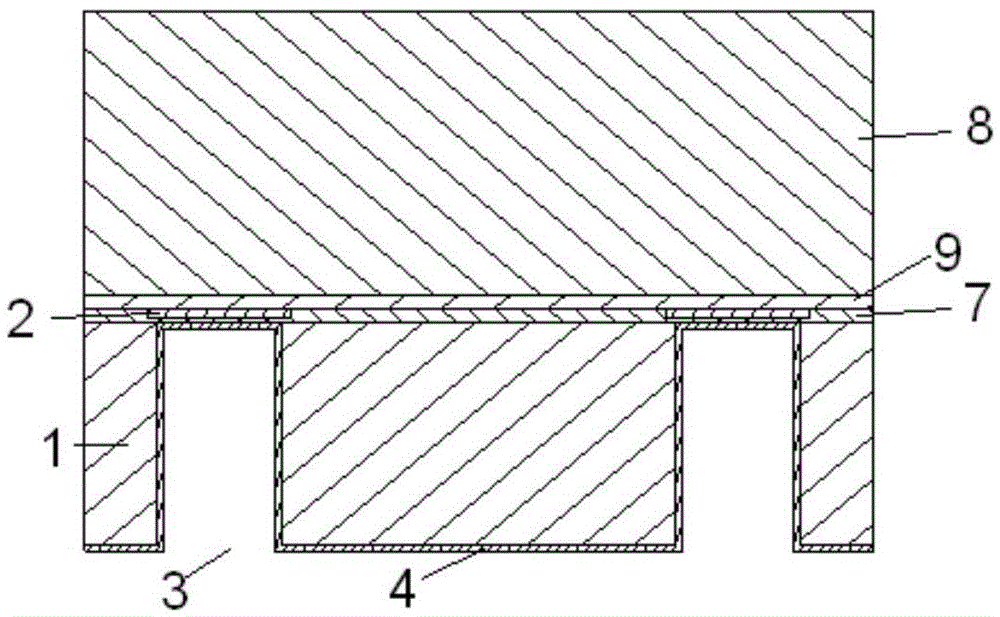

[0044] Such as Figure 7As shown, a low-cost chip back TSV interconnection structure includes at least one chip 1 with a bonding pad 2 on the front, and a through hole 3 corresponding to the bonding pad is formed on the back of the chip, and the through hole The bottom opening exposes the pad and the size is smaller than the size of the pad; the back of the chip and the sidewall of the through hole are covered with an insulating layer 4; the surface of the pad exposed by the bottom opening of the through hole is covered with A metal layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More