Trap state regulation and control based nonvolatile multi-bit micro/nanometer resistive random access memory and use method therefor

A resistive variable memory, non-volatile technology, applied in the direction of electrical components, etc., can solve difficult problems such as multi-bit storage performance, achieve good environmental compatibility, good compatibility, and realize the effect of efficient utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

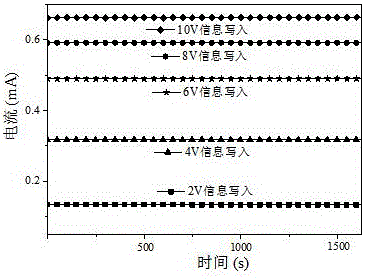

[0046] figure 2 After the micro / nano resistive memory of the present invention is written in 2V, 4V, 6V, 8V, 10V voltage, the memory performance test is performed. Adjust the function generator connected to the electrodes at both ends of the micro / nano resistive variable memory to a reading voltage of 0.5V, and then adjust the voltage to a writing voltage, and the writing voltage is 2V, 4V, 6V, 8V, 10V, after the voltage information is written, adjust back to the read voltage of 0.5V. Such as figure 2 As shown, after the voltages of 2V, 4V, 6V, 8V, and 10V are written, the micro / nano resistive memory has different resistance states. Sn-doped ZnO micro / nanowires have trap levels such as impurity levels, surface states, and intrinsic defects, and different write voltages can fill trap levels of different depths. When the trap is filled with electrons, the resistance state of the micro / nano resistive memory changes.

Embodiment 2

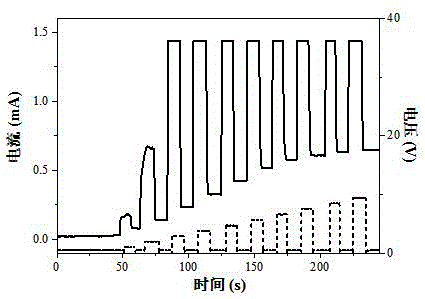

[0048] image 3 It is a diagram of the change of current with time after the voltage of 2V, 4V, 6V, 8V, and 10V is written in the micro / nano resistive memory of the present invention. Specifically, first adjust the function generator connected to the electrodes at both ends of the micro / nano resistive variable memory to a reading voltage of 0.5V, then adjust the writing voltage to 2V, 4V, 6V, 8V, and 10V respectively, and wait for the voltage information After writing, adjust back to the reading voltage of 0.5V and test the stability of the device current increasing with time. Such as image 3 As shown, after the voltages of 2V, 4V, 6V, 8V, and 10V are written, the holes in the traps are filled with electrons, the writing voltage is removed and the reading voltage is applied. The write voltage has a specific resistance state, and the resistance state can be maintained for a long time. When the holes in the trap are filled with electrons, the electrons are localized by the t...

Embodiment 3

[0050] Figure 4 to Figure 8 It is the repeatable reading and writing performance test of the micro / nano resistive memory of the present invention when the writing voltage is 2V, 4V, 6V, 8V, and 10V. Specifically: step 1, adjust the function generator connected to the electrodes at both ends of the micro / nano resistive variable memory to a reading voltage of 0.5V, and then adjust the voltage to 2V, 4V, 6V, 8V, and 10V for information writing input; Step 2, adjusting the voltage across the micro / nano resistive variable memory back to a voltage of 0.5V to read information; Step 3, placing the micro / nano resistive variable memory in a 70°C environment for signal erasing; Step 4, return to room temperature, and the resistance state of the micro / nano resistive variable memory returns to the initial state; repeat the cycle from step 1 to step 4 to detect the repeatability of the micro / nano resistive variable memory, except for the write voltage, all steps The reading voltage is a D...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More