A semiconductor power device layout

A power device and semiconductor technology, applied in the field of semiconductor power device layout, can solve problems such as excessive stress, increased chip thermal stress, and difficulty in continuing subsequent processes.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

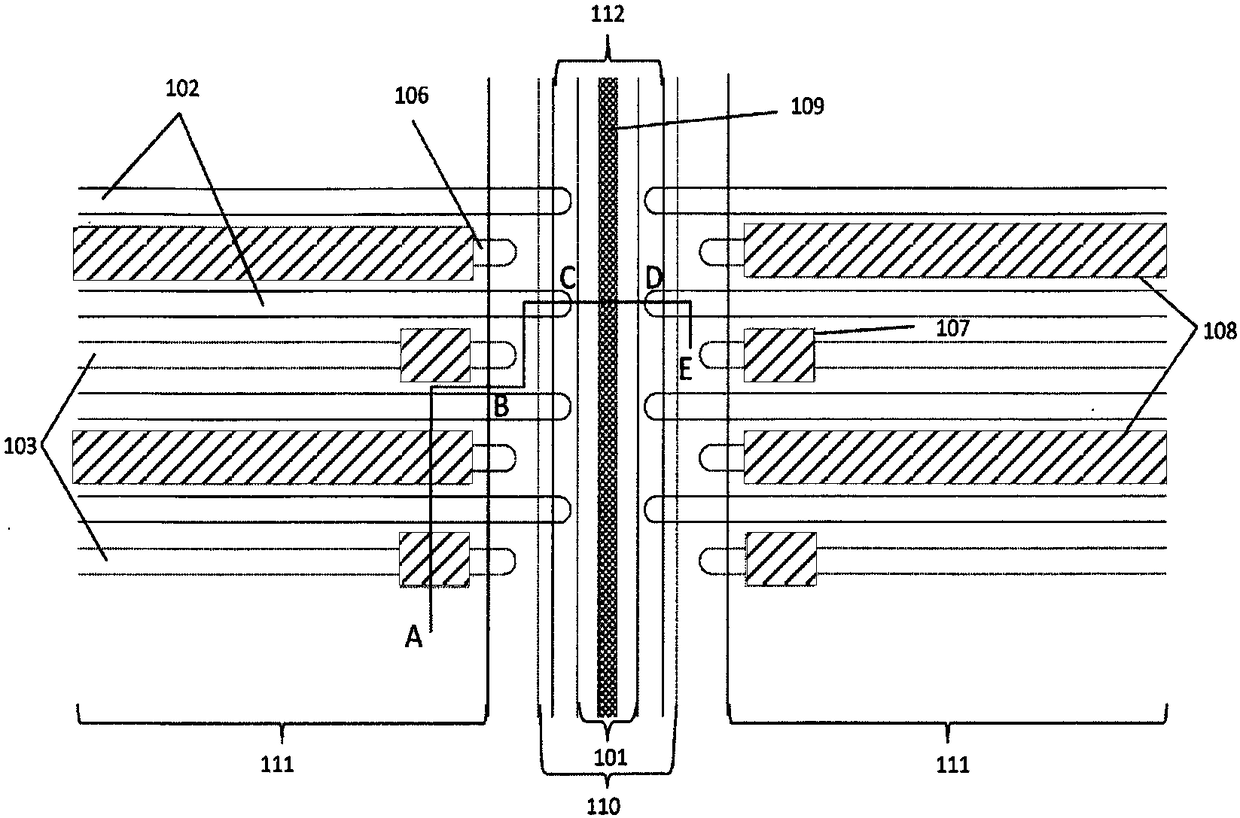

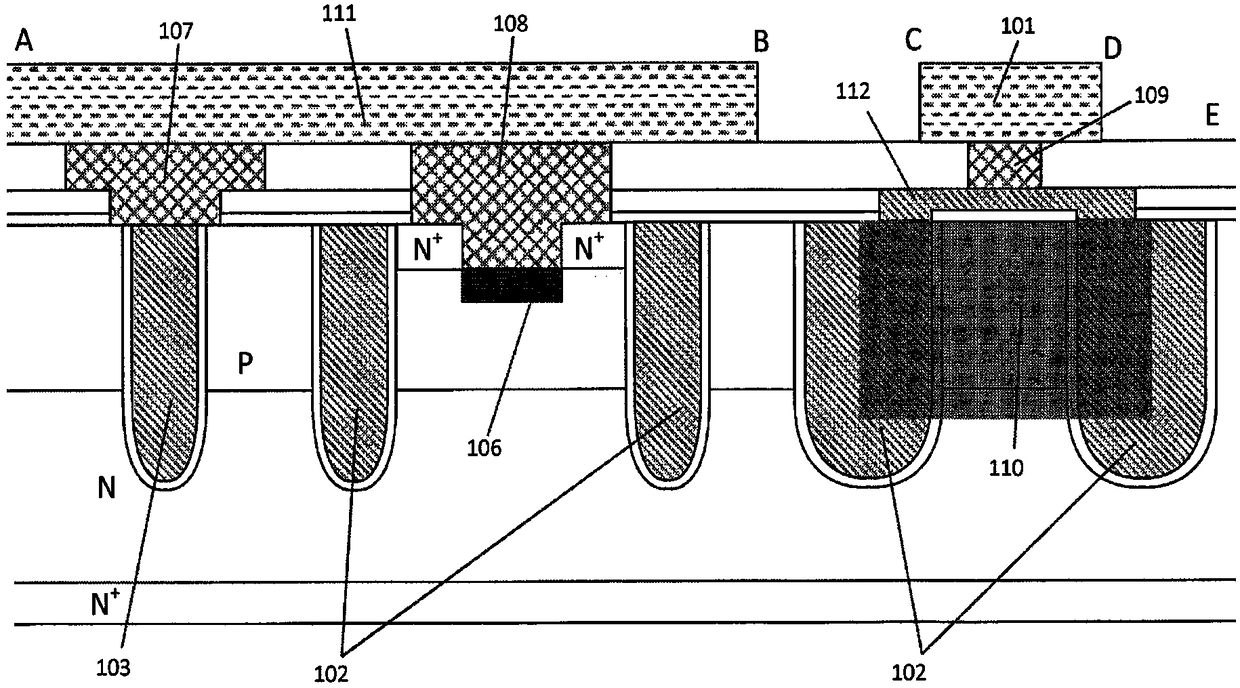

[0030] As mentioned in the background technology section, the gate trenches and dummy gate trenches of power MOSFETs in the prior art are all along a single horizontal direction, making the problem of excessive stress more serious. When the trenches are filled with an oxide layer , polysilicon and other substances, the accumulation of stress may cause the wafer to warp, making it difficult to continue the subsequent process. Width, because the dummy gate region is P-type, a large number of hole carriers are transported between the dummy gate region, the P+ gate contact region and the source region, which not only affects the performance and reliability of the device, but also causes uneven local current distribution on the chip. Both, increasing the thermal stress on the chip.

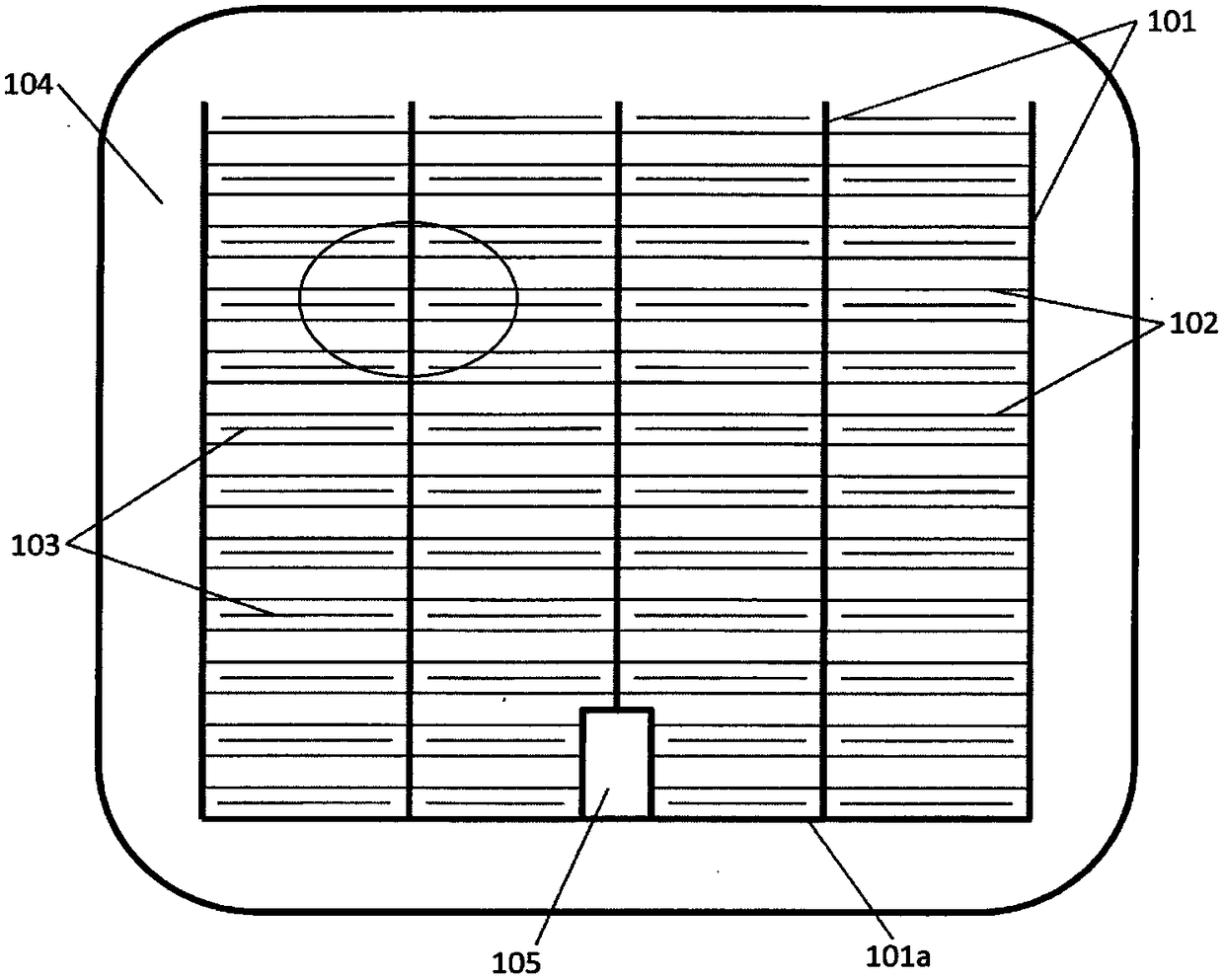

[0031]Based on this, an embodiment of the present invention provides a layout of a semiconductor power device, including a gate trench, a dummy gate trench, a base contact region, a dummy gate contact ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More