Semiconductor wafer, flattening method therefor, and packaging method

A packaging method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as reducing alignment accuracy and packaging strength, increasing wafer spacing difference, affecting chip quality, etc., to improve cutting effect, reduce pitch difference, and improve packaging effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

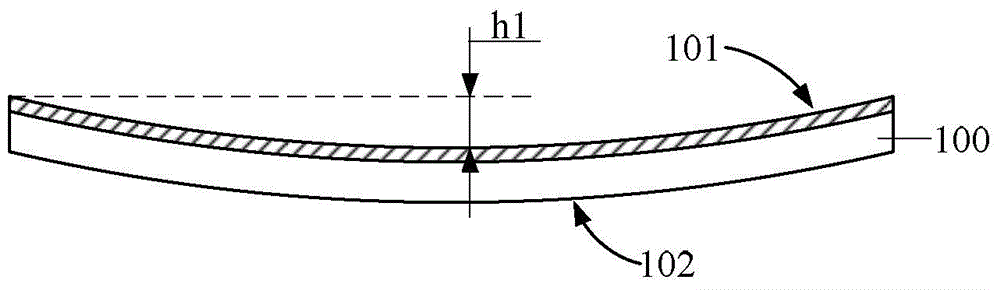

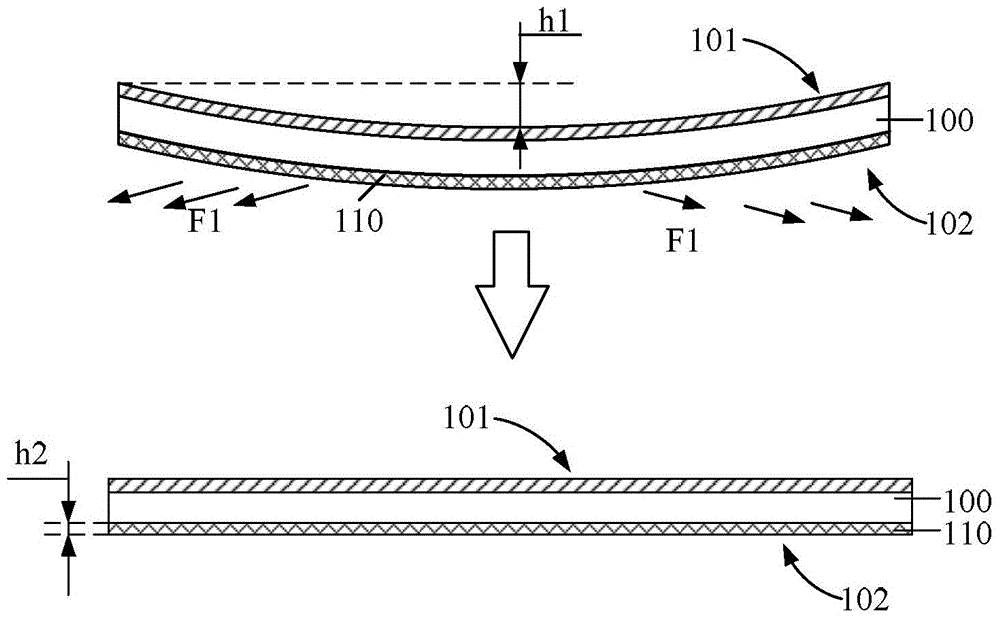

[0049] refer to figure 1 and figure 2 It is a cross-sectional view of a semiconductor wafer in different steps in this embodiment.

[0050] This implementation of the leveling method of the semiconductor wafer specifically includes:

[0051] first referencefigure 1 1. A semiconductor wafer 100 is provided, and the semiconductor wafer 100 includes a functional surface 101 formed with several semiconductor chips (not shown in the figure) and a back surface 102 opposite to the functional surface 101 .

[0052] The material of the semiconductor wafer 100 includes various materials such as silicon, germanium, gallium arsenide or silicon germanium, and semiconductor wafer materials in the art are all suitable for the semiconductor wafer in the present invention, and the present invention is for the semiconductor wafer The material is not limited.

[0053] In this embodiment, the material of the semiconductor wafer 100 is silicon.

[0054] The semiconductor wafer 100 is warped, ...

Embodiment 2

[0089] refer to Figure 5 and Figure 6 It is a cross-sectional view of a semiconductor wafer in different steps in this embodiment.

[0090] The technical scheme of the flattening method of the semiconductor wafer provided in this implementation is substantially the same as that of the semiconductor wafer flattening method provided in Embodiment 1, including: the semiconductor wafer 200 provided includes a plurality of semiconductor chips (not shown in the figure) The functional surface 201 of the functional surface 201 and the back surface 202 opposite to the functional surface 201, the semiconductor wafer 200 has warping deformation, and then a stress layer is formed on the back surface 202 of the semiconductor wafer 200 to realize the stability of the semiconductor wafer 200. leveling.

[0091] The difference between this embodiment and embodiment 1 is:

[0092] In this embodiment, before the stress layer is formed on the back surface of the semiconductor wafer 200, whe...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More