LDMOS device structure and manufacture method thereof

A technology of device structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of inability to achieve lithography size, etc., to solve the problem of lithography alignment accuracy, manufacturing yield and uniformity The effect of sexual security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

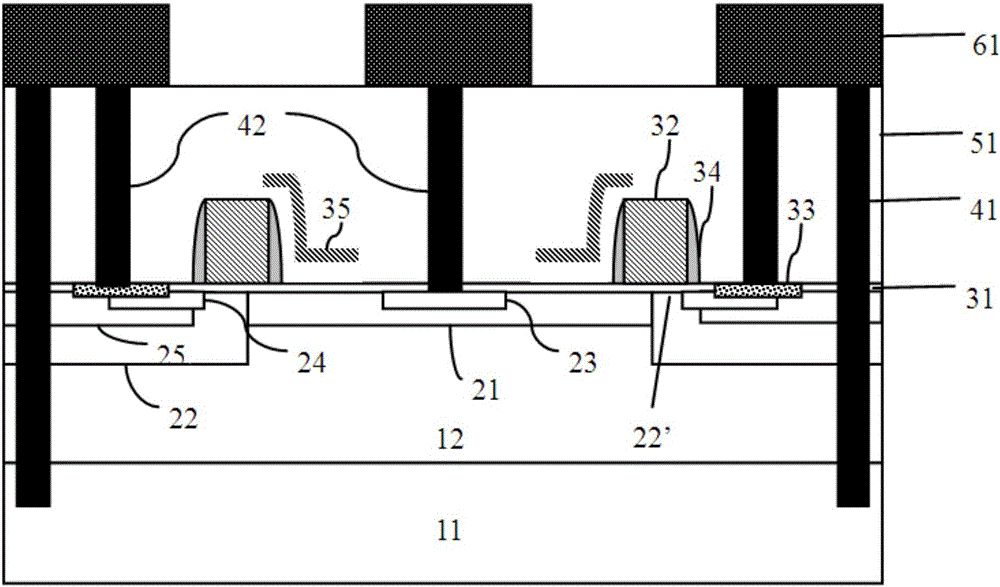

[0036] like figure 1 As shown, an LDMOS device structure includes a metal connection layer 41. The metal connection layer 41 connects the LDMOS device source 24 from the surface to the substrate 11. The material of the metal connection layer 41 is tungsten or copper, and Ti / TiN is used as the contact layer and the blocking layer, the channel is a concentration gradient channel, the channel is a P-type channel, the concentration of the channel near the source 24 is high, and the gate length of the LDMOS device is 90-250nm.

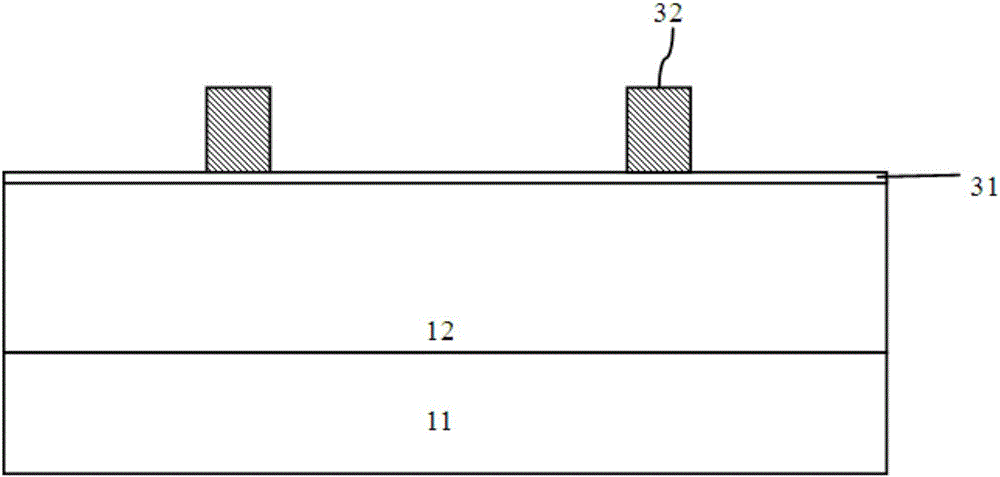

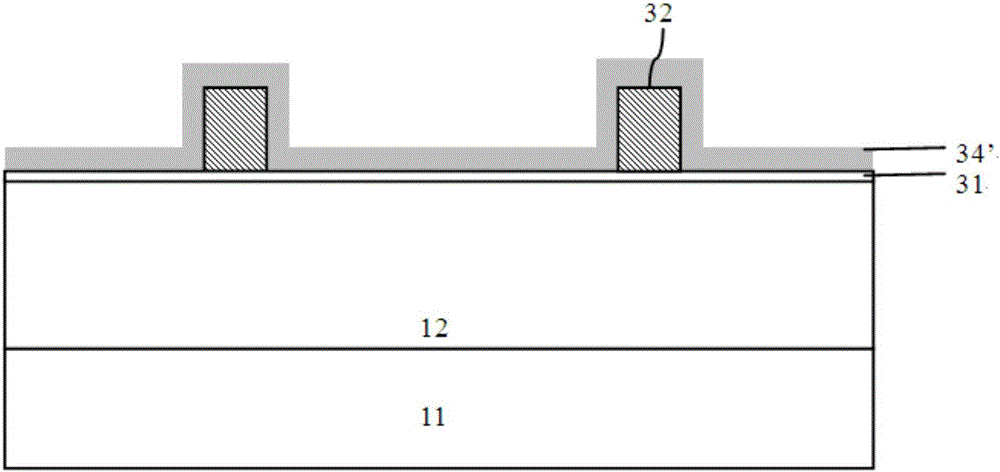

[0037] A method for fabricating an LDMOS device structure, comprising the following steps:

[0038] Step 1, gate oxide and gate deposition;

[0039] Step 2, after gate etc...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| cover factor | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More