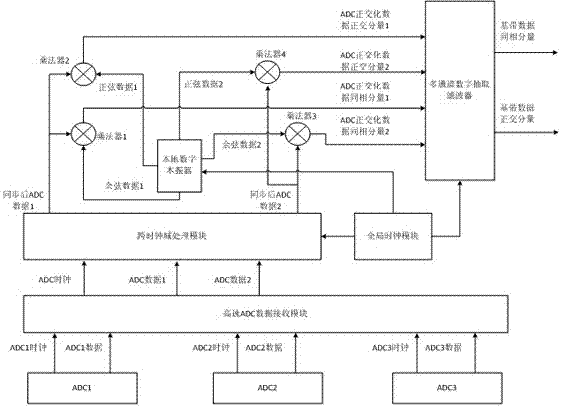

Method and system for realizing ultra-high-speed digital quadrature down-conversion and decimation filtering in FPGA

A technology of digital quadrature and decimation filtering, which is applied in transmission systems, digital technology networks, impedance networks, etc., can solve problems such as difficult design, achieve the effects of shortening the development cycle, improving scalability, and stably receiving and processing data

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] 1) AD device selection strategy

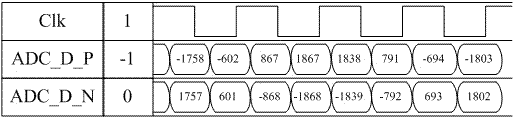

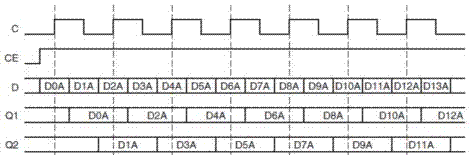

[0046] At present, there are three main types of external output data interfaces of high-speed AD conversion devices (Analog–to-Digital Converter hereinafter referred to as ADC): parallel LVTTL single-ended level output; serial LVDS differential level; and parallel LVDS differential level. Among these three types, LVTTL single-ended level is generally only used in occasions where the frequency does not exceed 100MHz due to its push-pull output architecture. This interface is rarely seen in ultra-high-speed AD devices. Typical products such as Linear Technology The LTC2208; the serial LVDS differential level only uses a pair of high-speed LVDS differential ports to complete data transmission, which greatly reduces the data port occupation. It is often used in single-chip multi-channel AD devices. The typical product is AD9259 from Analog Devices. However, when When the ADC sampling frequency is high, the operating frequency of serial LVD...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More