Through-silicon-via forming method and chip with through-silicon-via

A technology of through-silicon vias and chips, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of deposition, difficult to complete film formation, and easy falling off of conductor layers.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

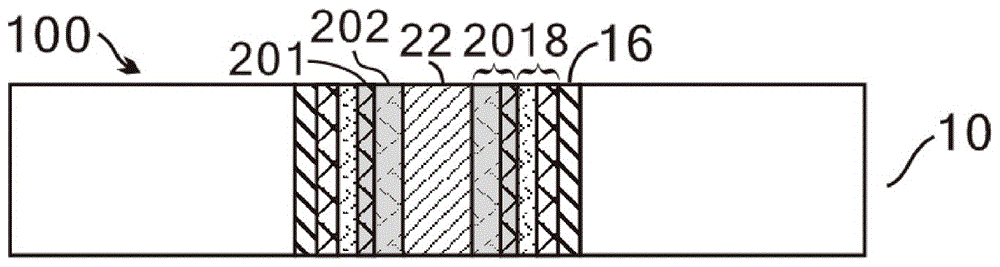

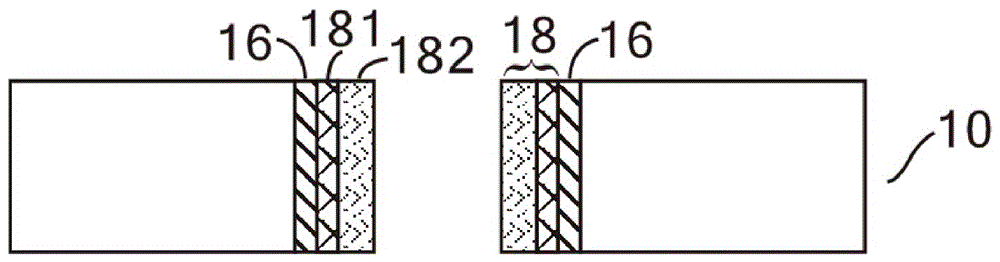

[0044] Hereinafter, embodiments of the present invention will be described in detail with reference to the accompanying drawings. It should be understood by those skilled in the art that these descriptions only illustrate exemplary embodiments of the present invention, and are not intended to limit the protection scope of the present invention. For example, elements or features described in one figure or embodiment of the invention may be combined with other elements or features described in one or more other figures or embodiments. In addition, in order to facilitate the description of the positional relationship between the various material layers, spatially relative terms are used herein, such as "upper" and "lower", and "inner" and "outer", etc., these terms are relative to the substrate. In terms of the surface or pore wall. For example, material A is considered to be above or outside material B if it is located in a direction toward the exterior of the substrate or pore...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More