Methods to improve die edge yield

A yield, edge-to-edge technology, used in electrical components, circuits, semiconductor/solid-state device manufacturing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

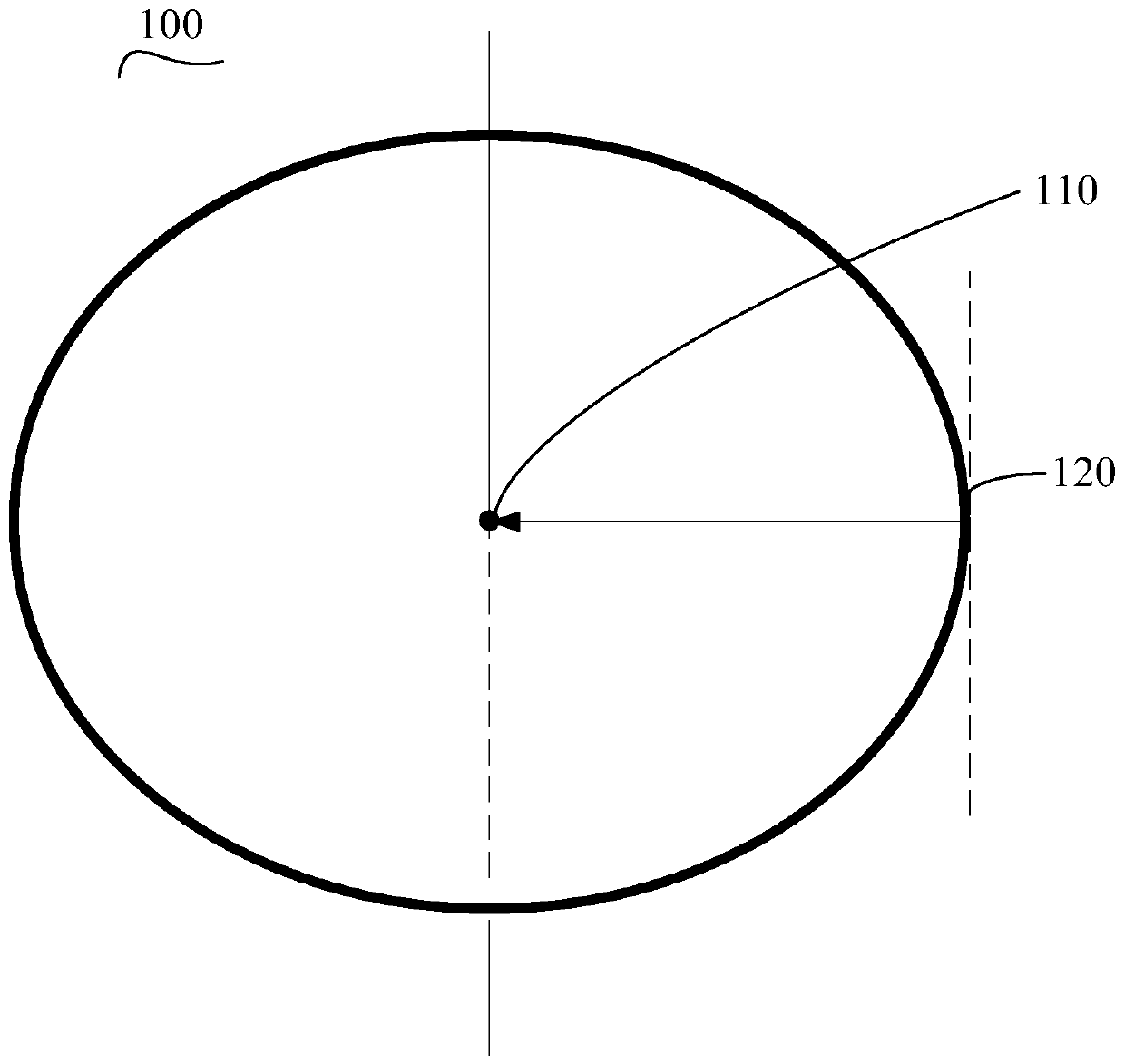

[0025] S110, a wafer substrate 100 is provided.

[0026] The specific type of substrate to be selected can be determined according to product requirements, including the material, crystal orientation, and doping type of the substrate, which are not limited here. Silicon substrates are commonly used in this field.

[0027] S120, photolithography forming a first photoresist layer.

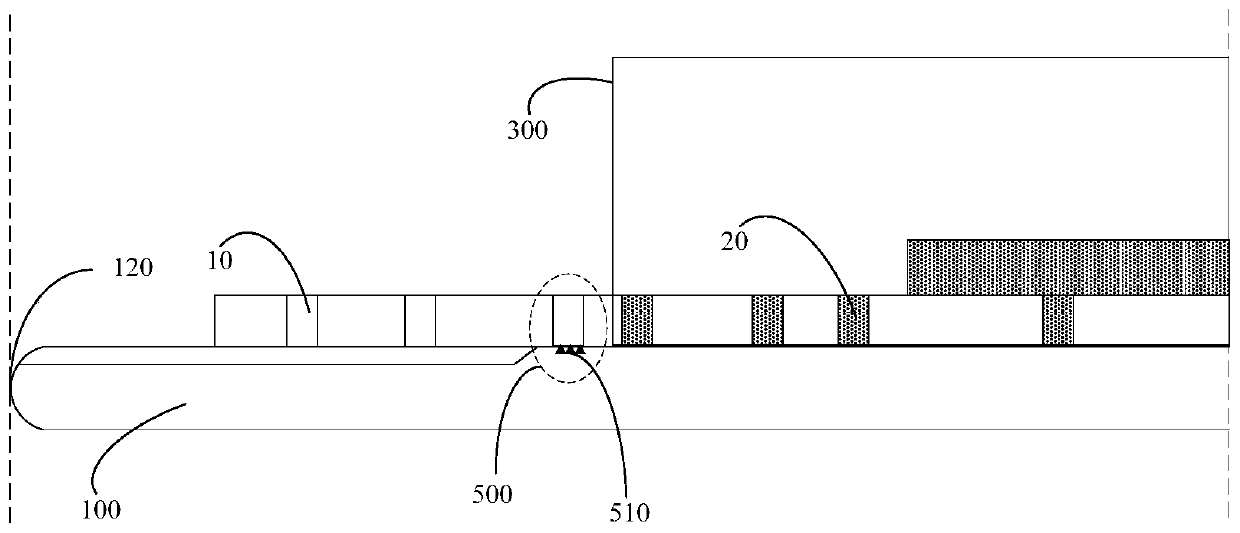

[0028] See also Figure 5 , Applying glue on the wafer substrate 100 to form a first photoresist layer 210, and performing edge washing of the active area (using an organic solvent to remove the photoresist residue on the edge of the wafer) and photolithography. In this embodiment, the edge washing dimension a1 in the direction from the edge 120 of the wafer substrate to the axis 110 of the wafer substrate is large enough so that the area where the photoresist is washed away at least extends from the edge of the wafer to the subsequent metal deposition Process deposition area 300.

[0029] S130, forming a ...

Embodiment 2

[0046] Embodiment 1 protects the substrate by forming an oxide layer under the unfilled contact holes 10, and embodiment 2 removes excess ILD so that no contact holes are formed outside the deposition area 300, thereby preventing the slurry from passing through the contact holes 10The hidden dangers of corrosion of the substrate.

[0047] Therefore, the main difference between the second embodiment and the first embodiment is that the edge washing dimension a2 in the direction from the edge 120 of the wafer substrate to the axis 110 of the wafer substrate is reasonably set in step S160, so that the photoresist is washed away. It extends at least from the edge of the wafer to the deposition area 300. In this way, in step S170, the excess interlayer dielectric 220 will be etched away, directly avoiding the generation of the contact hole 10 that is not filled with metal. Such as Figure 7 Shown.

[0048] Similar to the embodiment 1, after step S190, a step of forming a metal connec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com