Circuit-level modeling method and model circuit which are used for GGNMOS

A modeling method and circuit technology, applied in CAD circuit design, electrical digital data processing, special data processing applications, etc., can solve problems such as low efficiency, time-consuming physical-level modeling, and increased design costs, achieving high efficiency, Simple structure and low design cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0049] Embodiment: Taking SMIC65nm process standard IO as an example, how to realize the equivalent circuit model of GGNMOS in the present invention is illustrated.

[0050] Figure 4 It is the GGNMOS schematic diagram of the standard IO provided by the SMIC process, such as Figure 4 As shown, the peripheral ring P+sub-ring represents the P-type implanted substrate ring, which is divided into three regions A, B, and C, including 18 GGNMOS devices, numbered Q0-Q17 respectively, and the GNNMOSs in each region are connected in parallel. relation.

[0051] Figure 5 yes Figure 4 In the connection relationship between the ports of each device of Q0-Q17, the gates, sources and substrates of the GGNMOS devices Q0-Q17 are all connected to the power ground, and the drains are connected to the power potential.

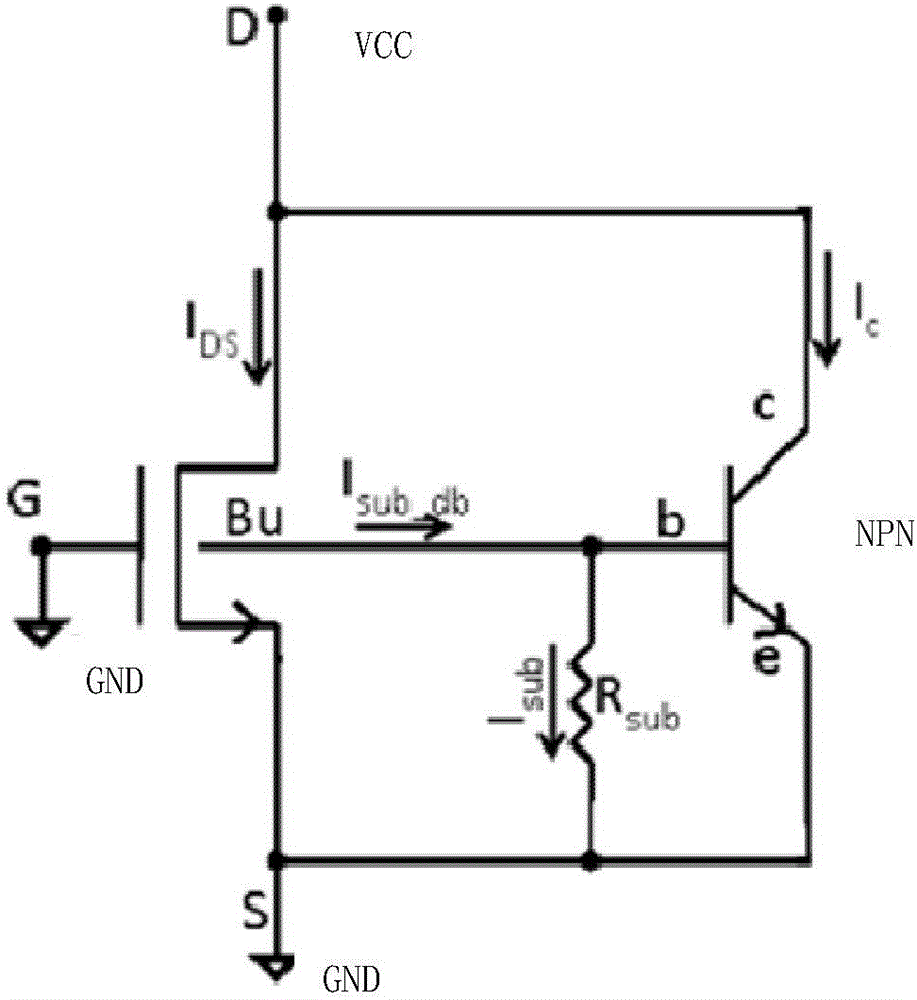

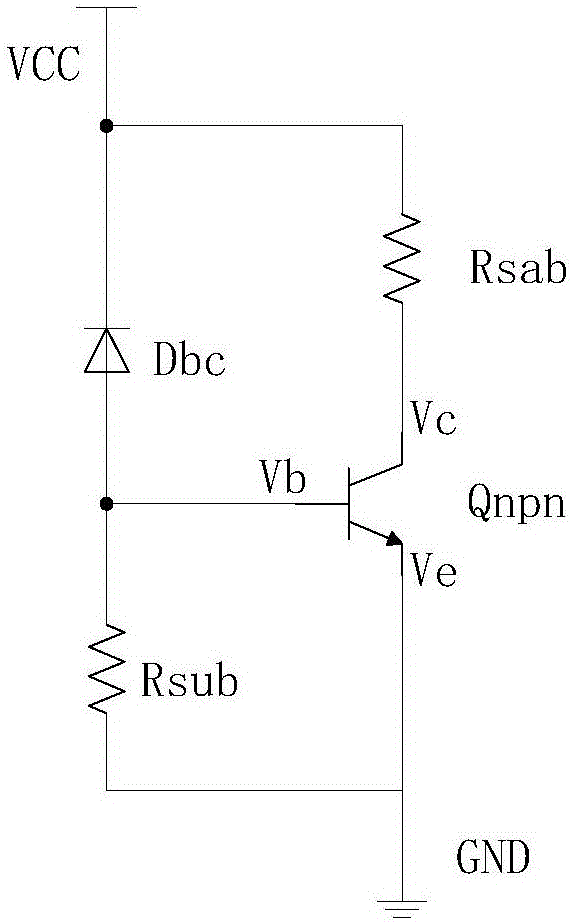

[0052] Image 6 yes figure 1 The enlarged view of the area A in the middle, SAB represents the silicide barrier layer of the drain region, ESD1 represents the ESD inject...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More