FPGA-based algorithm library simulation and verification platform implementation method

A simulation verification and implementation method technology, which is applied in the field of FPGA-based algorithm library simulation verification platform, can solve the problems of test time and error probability increase, and achieve the effect of shortening the simulation verification cycle, simple and unified interface, and more automatic simulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

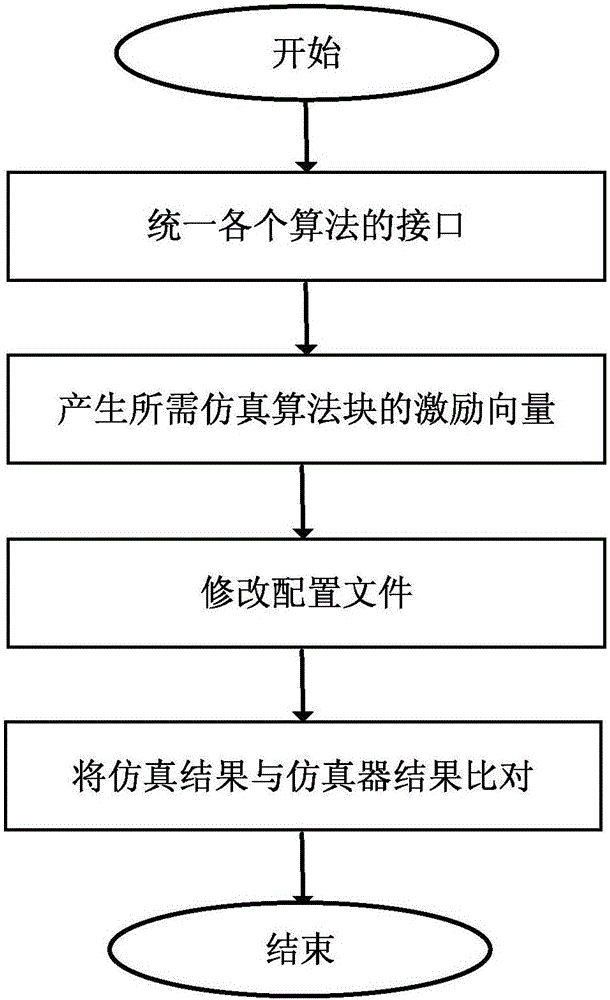

[0025] Such as figure 1 Shown, with a newly added four input adder algorithm block as example, the present invention is described in detail, and its implementation steps are as follows:

[0026] Step 1: Add the inputs of the four-input adder to the unified input data interface. The input data and output data register lengths are adjusted appropriately accordingly. Use a unified control signal.

[0027] Step 2: Generate several sets of test vectors according to the test requirements, and use the matlab emulator to store all decimal adder inputs in floating-point number IEEE754 format;

[0028] Step 3: Include the source file and test vector of the adder into the algorithm library verification platform, modify the configuration file of the adder in the platform, and the newly added algorithm block of the adder will be added automatically, no need to do interface Any changes, output simulation results;

[0029] Step 4: The script file of the FPGA simulation tool modelsim will...

Embodiment 2

[0031] Such as figure 1 As shown, taking a newly added divider algorithm block as an example, a kind of FPGA-based algorithm store simulation verification platform implementation method of the present invention is described, and its implementation steps are as follows:

[0032] Step 1: Add the inputs of the four-input divider to the unified input data interface. The input data and output data register lengths are adjusted appropriately accordingly. Use a unified control signal.

[0033] Step 2: Generate several groups of test vectors according to the test requirements, and store all decimal divider input vectors in floating-point number IEEE754 format with the matlab emulator;

[0034] Step 3: Include the divider source file and test vector into the algorithm library verification platform, modify the configuration file of the divider in this platform, and the newly added divider algorithm block will be added automatically, no need to do interface Any changes, output simulat...

Embodiment 3

[0038] A method for realizing an FPGA-based intelligent simulation and verification platform for a nuclear safety level algorithm library of the present invention, the algorithm library is an application algorithm library for a nuclear power control system, which includes the following steps:

[0039] Step 1: According to the application requirements of the safety-level control system of nuclear power plants, all algorithm blocks are basically implemented by FPGA, and all algorithm blocks in the algorithm library are set to a unified interface;

[0040] Step 2: Generate simulation stimulus vectors for each algorithm block;

[0041] Step 3: If you need to add an algorithm block, you only need to add the content of the algorithm block and the corresponding simulation vector on the verification platform, and then modify the configuration file;

[0042] Step 4: Compare and analyze the simulation results output by the simulation tool and the results generated by the simulator.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com