SIP module testing method based on on-chip embedded microsystem

A module testing, module internal technology, applied in the direction of analog/digital conversion calibration/testing, electronic circuit testing, measuring electricity, etc., to achieve the effect of test optimization, improve test efficiency, improve efficiency and test effectiveness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The method of the present invention is based on the designer, and the production links are not within the scope of the invention. The test design method adopting the SIP module of the present invention includes two parts: hardware test platform design and software test scheme design. The involvement between the two parts of the design is relatively large, and it needs to be coordinated at the same time.

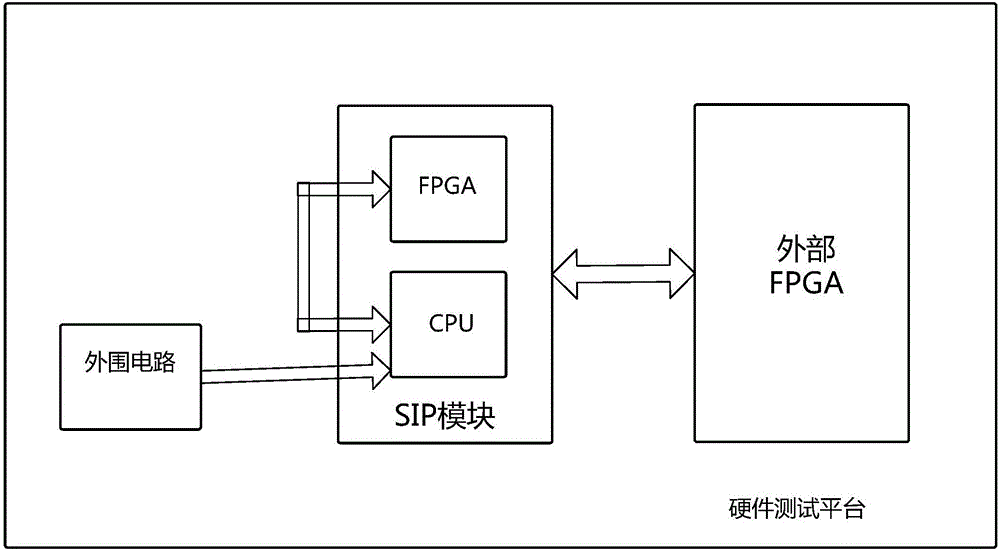

[0024] figure 1 For the hardware test platform design schematic diagram of the present invention, peripheral circuit provides system resources (electrical signal, ground signal, clock signal, etc.) and board-level interconnection for whole board (comprising device under test); CPU pin in SIP module is connected with internal FPGA , can test the corresponding pins of CPU and FPGA; the external FPGA chip receives part of the output signal of the SIP module, and accesses the output signal result for the test system to read.

[0025] A kind of SIP module test method base...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More