Packaging structure of a semiconductor chip

A packaging structure and semiconductor technology, applied in the field of microelectronics, can solve problems such as uneven heat dissipation of semiconductor chips, and achieve the effects of solving uneven heat dissipation, increasing area, and reducing thermal resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

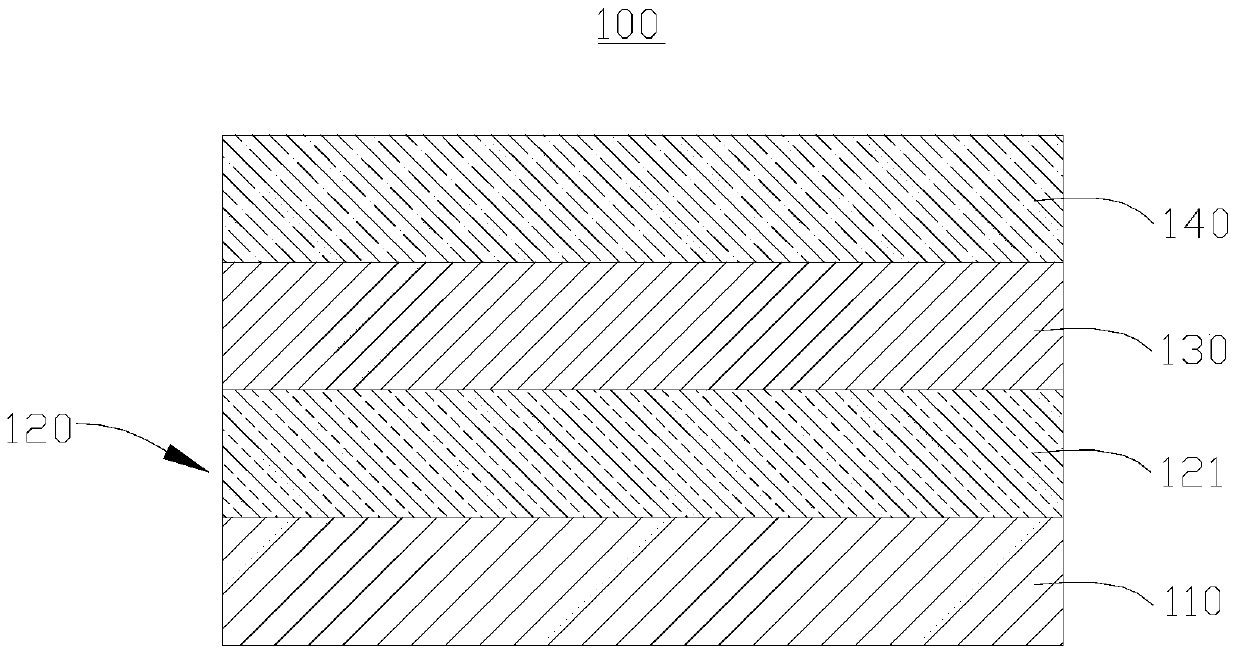

[0038] see figure 1 , The packaging structure 100 for semiconductor chips provided in this embodiment includes: a metal carrier layer 110 , a first thermal diffusion layer 120 , a thermally conductive adhesive layer 130 and a semiconductor chip 140 . The first thermal diffusion layer 120 is located on the metal carrier layer 110 , the thermally conductive adhesive layer 130 is located on the first thermal diffusion layer 120 , and the semiconductor chip 140 is located on the thermally conductive adhesive layer 130 . That is, both the first thermal diffusion layer 120 and the thermally conductive adhesive layer 130 are located between the metal carrier layer 110 and the semiconductor chip 140 .

[0039] In this embodiment, the first thermal diffusion layer 120 is a graphene layer 121, and the graphene layer 121 is made of graphene. Graphene is a flat film of carbon atoms that can be as thin as one carbon atom thick. The plane thermal conductivity of graphene is very good, and...

no. 2 example

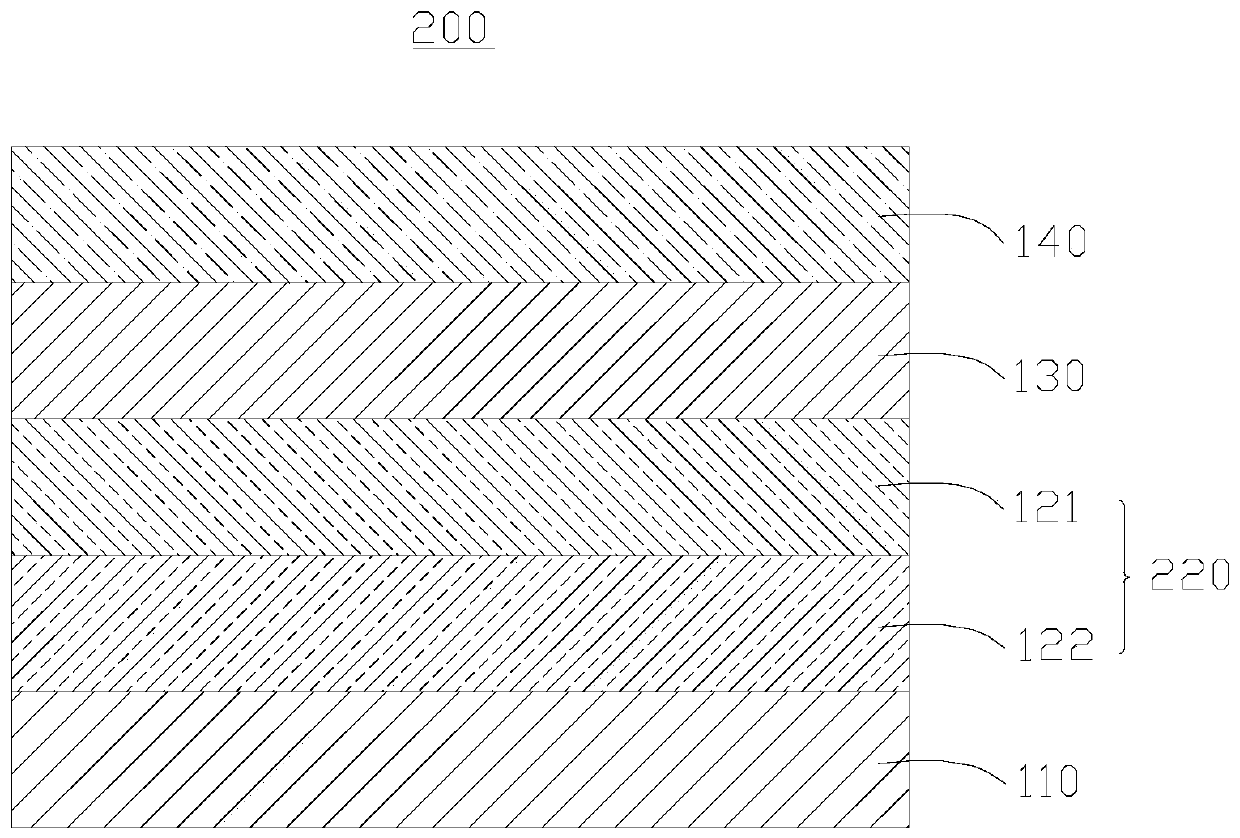

[0048] see figure 2 The semiconductor chip packaging structure 200 provided in this embodiment is substantially the same in structure as the semiconductor chip packaging structure 100 provided in the first embodiment. The difference between them is that, in this embodiment, the first thermal diffusion layer 220 includes a graphene layer 121 and a metal bonding layer 122 , and the metal bonding layer 122 is located between the graphene layer 121 and the metal carrier layer 110 . In this embodiment, the number of metal bonding layers of the first thermal diffusion layer 320 is equal to the number of graphene layers, and one layer of graphene layer 121 and one layer of metal bonding layer 122 are stacked to form a metal carrier layer 110. The first thermal diffusion layer 220 . Specifically, the metal bonding layer 122 may be made of copper, aluminum, copper molybdenum, copper tungsten, and the like. Copper, aluminum, copper molybdenum and copper tungsten not only have better ...

no. 3 example

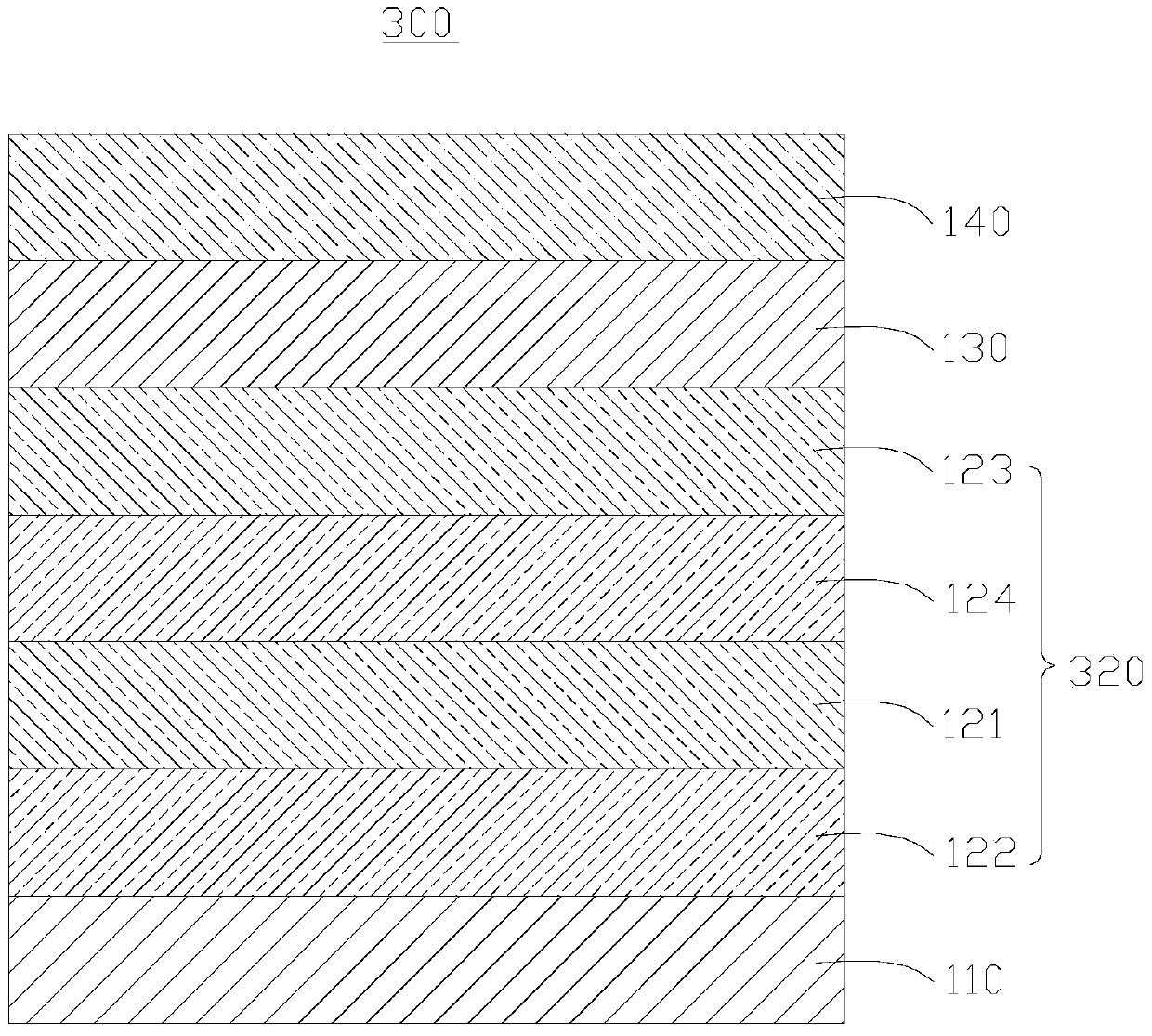

[0050] see image 3 The semiconductor chip packaging structure 300 provided in this embodiment is substantially the same in structure as the semiconductor chip packaging structure 200 provided in the second embodiment. The difference between the two is that, in this embodiment, the first thermal diffusion layer 320 includes a graphene layer 121 , a metal bonding layer 122 , a graphene layer 123 and a metal bonding layer 124 that are stacked on top of each other. The first thermal diffusion layer 320 is located between the thermally conductive adhesive layer 130 and the graphene layer 121 . Specifically, the graphene layer 123 is located on the metal bonding layer 124, and between the thermally conductive adhesive layer 130 and the metal bonding layer 124, and the metal bonding layer 124 is located on the graphene layer 121, and is positioned between the graphene layer 123 and graphite. Between the graphene layer 121, the graphene layer 121 is located on the metal bonding laye...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More