Method for realizing high performance of radix-2 one-dimensional FFT (Fast Fourier Transform) based on domestic SW 26010 processor

An implementation method and processor technology, applied in the field of Fourier transform, can solve problems such as low performance, achieve the effects of improving performance, solving limited memory access bandwidth, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

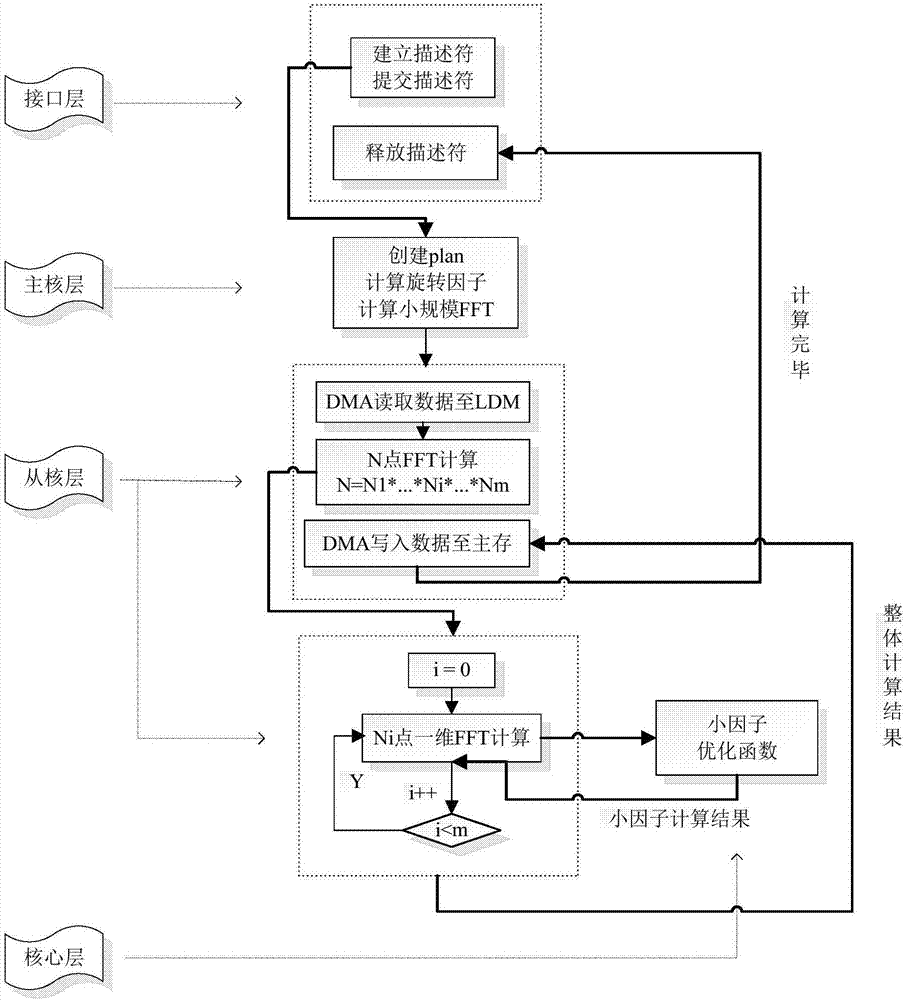

[0031] Such as figure 1 As shown, the present invention is a high-performance implementation method of base-2 one-dimensional FFT based on the domestic Shenwei 26010 processor. The design framework includes four layers: interface layer, main core layer, slave core layer, and core layer. The calling relationship is the interface layer - master core layer - slave core layer - core layer, the core layer is called multiple times from the core layer. The interface layer establishes descriptors containing information such as input data size and data dimension; the main core layer is based on the descriptor information. When the input data size is greater than or equal to 512, the input sequence is decomposed. When the input data size is less than or equal to 256, it is directly in the Perform FFT calculation on the master core; the slave core layer is responsible for reading and storing main memory data and local memory data according to the data decomposition results of the master ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More