Circuit and method for testing cycle time of SRAM

A cycle time and circuit technology, applied in static memory, instruments, etc., can solve the problems of SRAM peripheral circuit failure, complex logic structure, and failure to test, etc., to shorten the overall test time, simplify the circuit logic structure, and avoid test errors Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

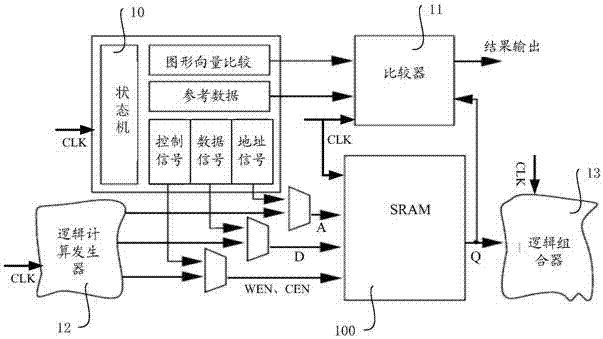

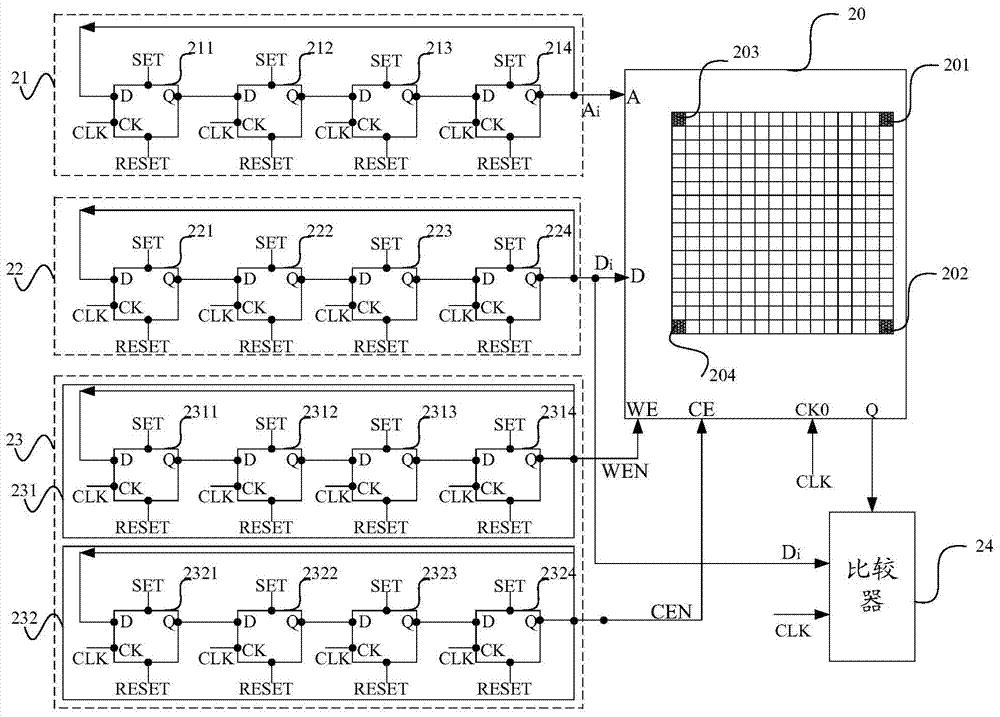

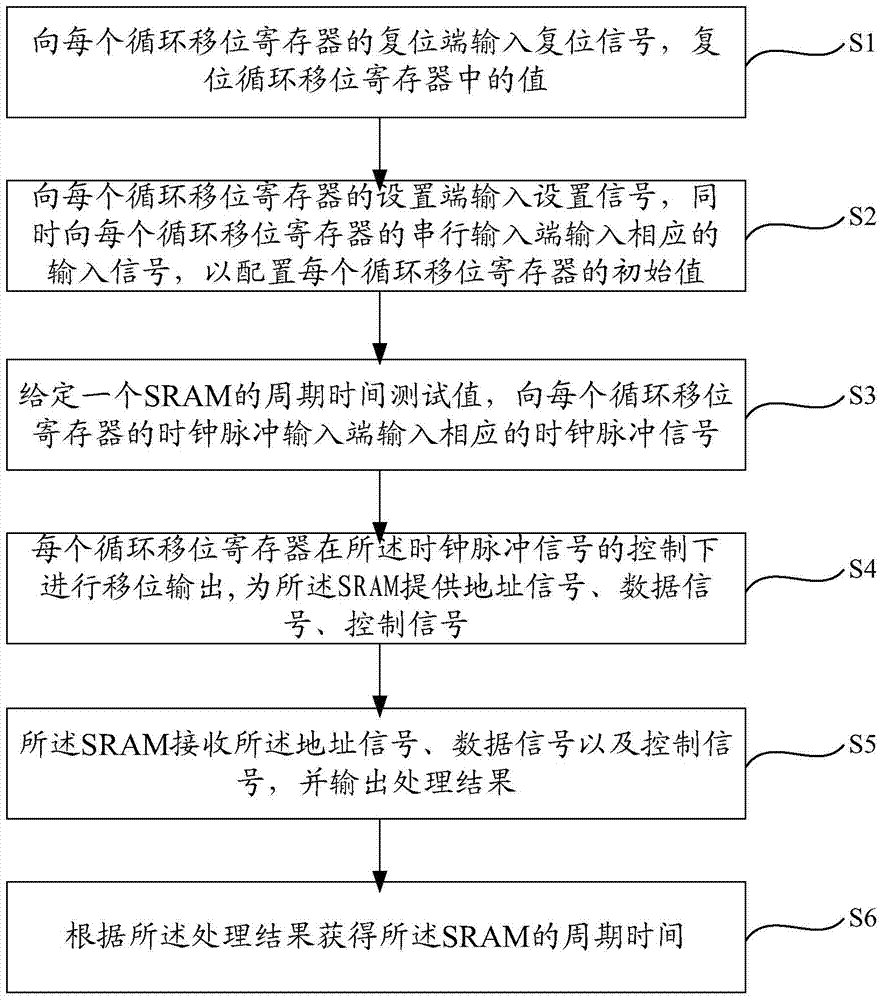

[0034] The core idea of the present invention is to build the signal generating circuit for SRAM testing by a pure cyclic register (pipeline shift) structure, that is, address cyclic shift registers, data cyclic shift registers and control cyclic shift registers are set. Pre-configure the values in each cyclic shift register to provide SRAM with different address signals, data signals, and control signals for testing, so as to realize the addressing and data reading of different storage units in sequence during the SRAM cycle time test , data writing and other operations, the logic structure of the new circuit is simple, the speed is fast, and the time and logic algorithm for generating the next address, data and control signal through calculation are avoided.

[0035] In order to make the purpose and features of the present invention more obvious and understandable, the specific implementation of the present invention will be further described below in conjunction with the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More