A graphene electrode MOS based on Ni catalysis 2 Field Effect Transistor Method

A technology of field-effect transistors and graphene electrodes, which is applied in the direction of circuits, electrical components, semiconductor devices, etc., can solve the problems of inapplicability to large-scale manufacturing and complicated preparation processes, and achieve the effect of solving photoresist residues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0025] The specific implementation steps are as follows:

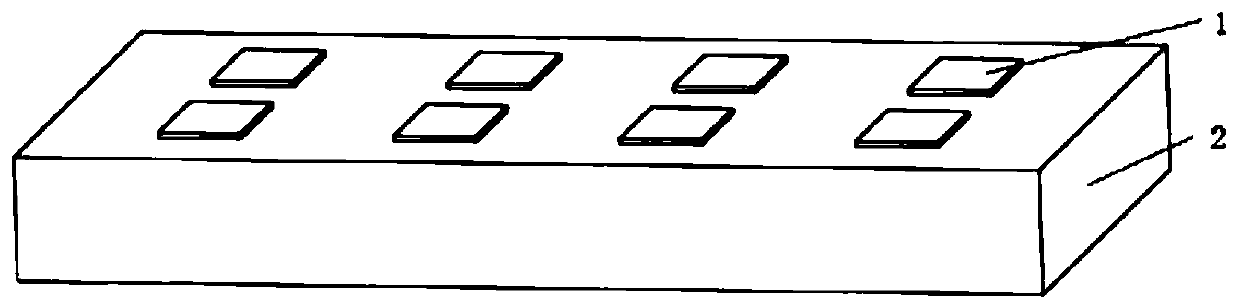

[0026] 1. On SiO 2 0.5~1µm polydimethylglutarimide (PMGI) and 20nm phenylpropanolamine hydrochloride (PPA) were deposited on the / Si substrate respectively, and a 5×10µm width was directly written by thermal scanning probe nanofabrication technology. Graphics, vapor deposition of Ni metal with a thickness of 500~800nm to form a patterned Ni catalytic nano-layer. Such as figure 1 shown.

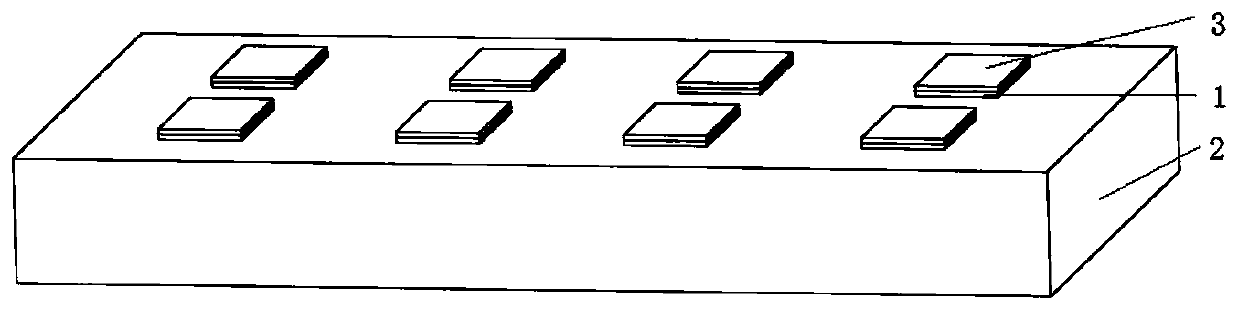

[0027] 2. Prepare SiO with Ni nano-layer 2 / Si substrate was soaked in acetic acid for 5~10min to remove the oxide on the surface of the Ni catalyst layer. The substrate was placed in a quartz tube furnace and evacuated to 10-6Torr, and H 2 / Ar (5% by volume) atmosphere at 1200~1500°C for 2 hours to remove impurities on the surface of the Ni nanolayer. Adjust the temperature to 1000~1200℃ and feed CH 4 , Ar, H 2 The mixed gas lasts for 30~60min. Stop CH 4 , cooled to get figure 2 The patterned graphene electrode is shown....

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com