Micro-electro-mechanical system chip and integrated circuit chip mixed packaging structure and packaging method thereof

A technology of micro-electromechanical chips and integrated circuits, which is applied in the direction of microstructure devices, manufacturing microstructure devices, and processing microstructure devices, etc., can solve the problems of low yield, low integration and difficult process, and achieve low cost and high integration. The effect of high and reduced dosage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

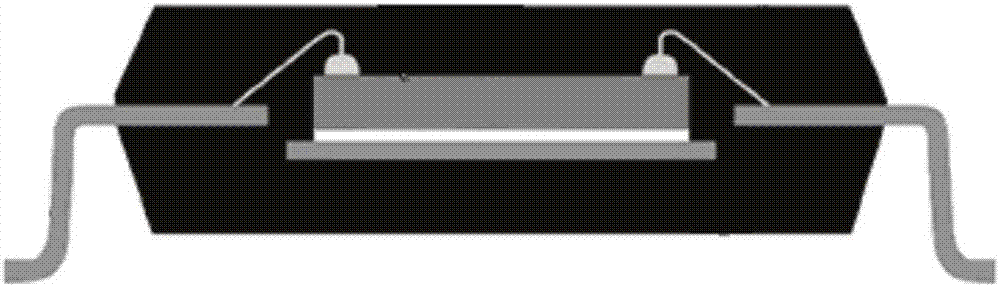

[0091] Such as Figure 5As shown, the hybrid packaging structure of micro-electromechanical chips and integrated circuit chips includes micro-electromechanical chips, integrated circuit chips, an upper substrate, a lower substrate, and a molding compound disposed between the upper substrate and the lower substrate. 4 integrated circuit chips, the 4 integrated circuit chips and the upper surface of the lower substrate are electrically connected through leads; a window is arranged on the upper substrate, and 3 micro-electromechanical chips are arranged in the window, and the connection between the 3 micro-electromechanical chips Electrical connections are formed between the upper substrate and the upper substrate through leads; epoxy solder flux filling materials are arranged between the upper substrate and the molding compound; electrical connections are realized between the upper substrate and the lower substrate through conductive through holes.

[0092] This embodiment only ...

specific Embodiment 2

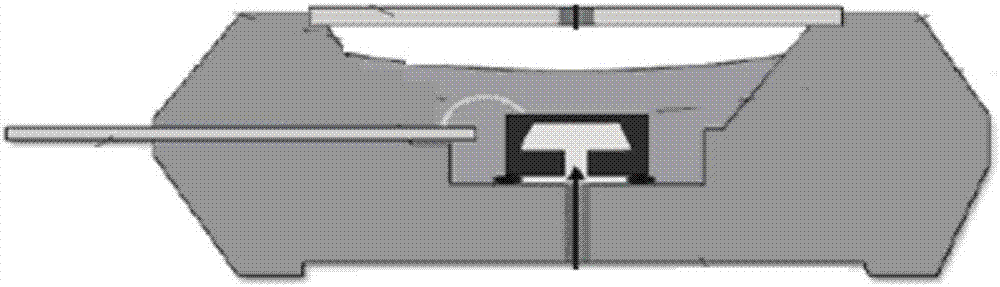

[0094] Such as Figure 6 As shown, the hybrid packaging structure of micro-electromechanical chips and integrated circuit chips includes micro-electromechanical chips, integrated circuit chips, an upper substrate, a lower substrate, and a molding compound disposed between the upper substrate and the lower substrate. 4 integrated circuit chips, the 4 integrated circuit chips and the upper surface of the lower substrate are electrically connected through leads; two windows are set on the upper substrate, one of which is equipped with 2 micro-electromechanical chips, and the other window A micro-electromechanical chip is arranged inside, and electrical connections are formed between the micro-electromechanical chips and the upper substrate through leads; epoxy flux filling material is arranged between the upper substrate and the molding compound; the upper substrate and the lower substrate are connected through conductive The through hole realizes the electrical connection.

[0...

specific Embodiment 3

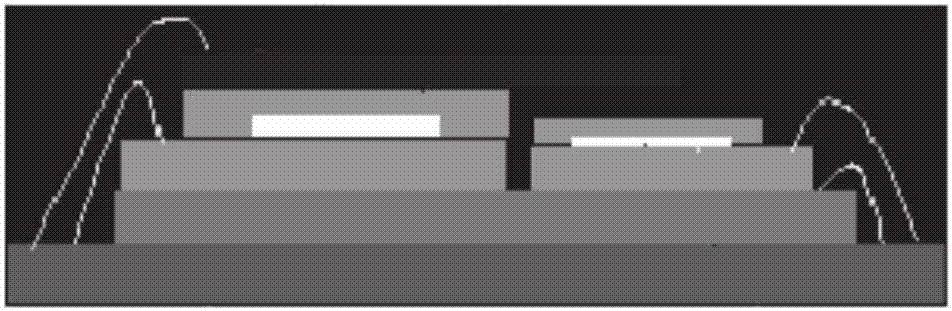

[0097] Such as Figure 7 As shown, the hybrid packaging structure of micro-electromechanical chips and integrated circuit chips includes micro-electromechanical chips, integrated circuit chips, an upper substrate, a lower substrate, and a molding compound disposed between the upper substrate and the lower substrate. 4 integrated circuit chips, the 4 integrated circuit chips and the upper surface of the lower substrate are electrically connected through leads; two windows are set on the upper substrate, one of which is a sunken window, and 2 windows are set in the sunken window. One microelectromechanical chip, the other window is a raised window, and a microelectromechanical chip is arranged in the raised window, and electrical connections are formed between the microelectromechanical chips and the upper substrate through leads; the upper substrate and the molding compound are arranged Epoxy solder flux filling material; electrical connection between the upper substrate and th...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap