Multi-octave ultra-broadband amplifier circuit

An amplifier circuit, ultra-broadband technology, applied in the direction of amplifier combination, improved amplifier to expand bandwidth, electrical components, etc., can solve the problems of low unit circuit gain, power consumption and large chip area, so as to reduce the impact and realize high frequency Bandwidth, to achieve the effect of expansion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

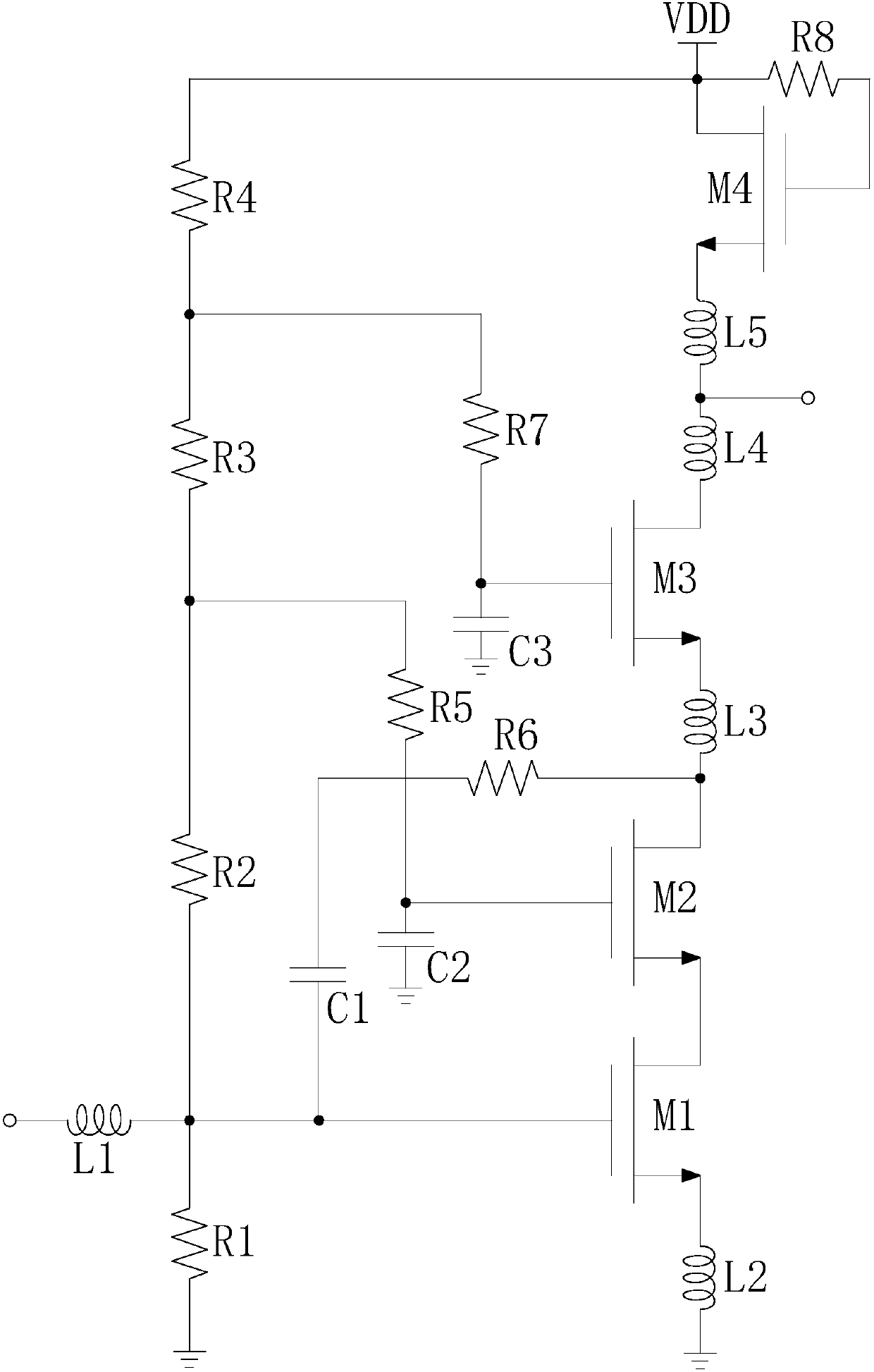

[0023] Such as figure 1 As shown, a multi-octave ultra-wideband amplifier circuit includes an input matching circuit, a cascode structure with three transistor stacks, a feedback circuit, a peaking inductor, an active-passive hybrid bias circuit, and a resistor Voltage divider network and power supply VDD, wherein, the transistors in the common source-common gate structure in this embodiment are any one of N-channel transistors, P-channel transistors, high electron mobility transistors and pseudo-high electron mobility transistors, figure 1 Shown is an N-channel transistor. The three transistors in the cascode structure of this embodiment are transistor M1, transistor M2, and transistor M3, the gate of transistor M1, the gate of transistor M2, the gate of transistor M3, and the active-passive hybrid bias The circuits are all connected to the power supply VDD, the source of the transistor M1 is grounded, as required by the cascode structure, the gate of the transistor M2 is gr...

Embodiment 2

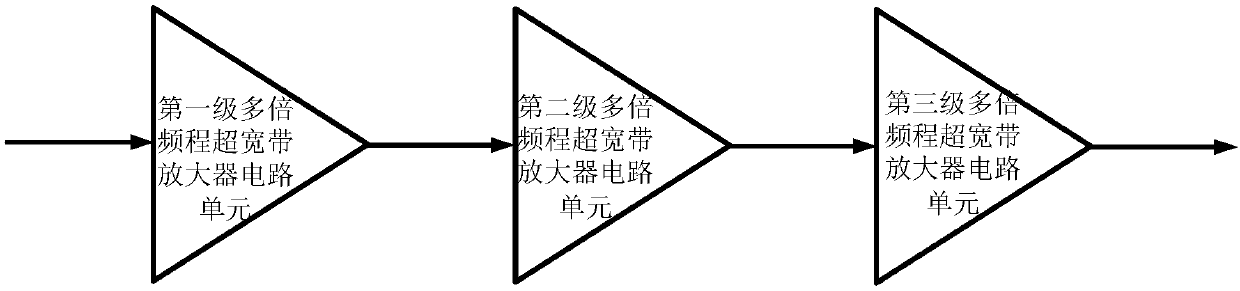

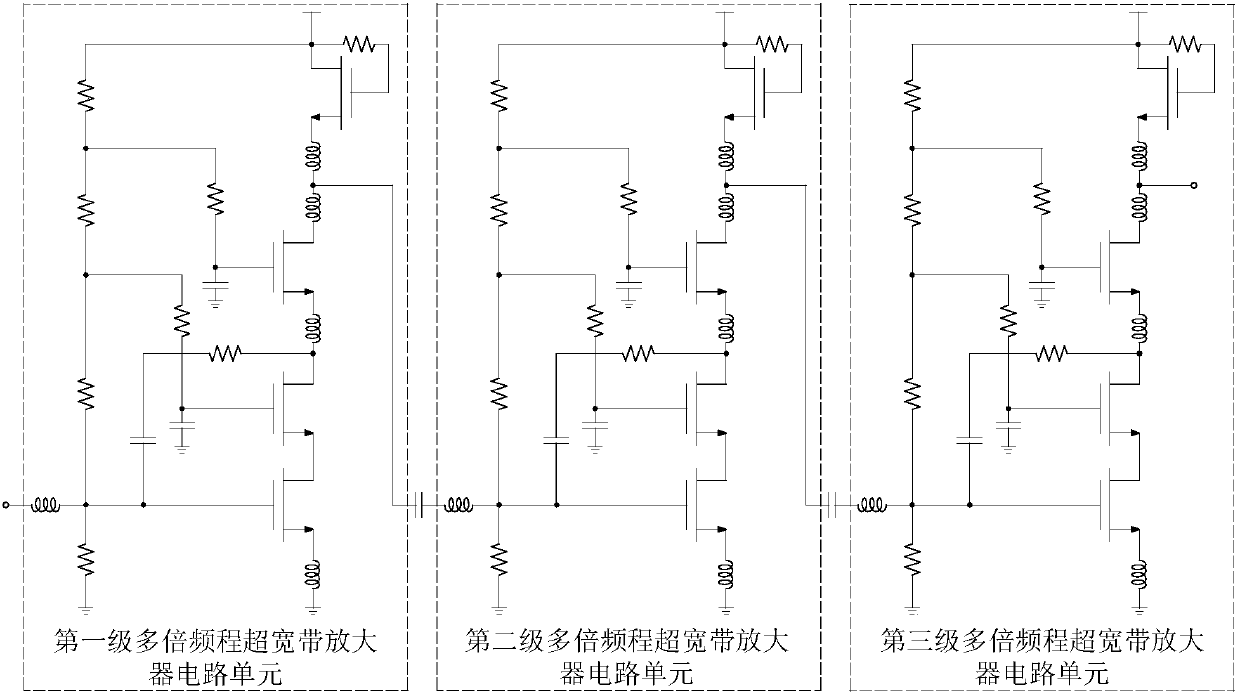

[0032] This embodiment makes the following further limitations on the basis of Embodiment 1: This embodiment cascades the amplifier circuit units in the three-stage implementation case 1 (the actual amplifier generally needs to be multi-stage cascaded to meet the requirements for gain, etc. The requirements of the index, each cascaded circuit is usually called an amplifier circuit unit), and its simulation results are given. figure 2 It is cascaded three levels figure 1 The circuit structure block diagram of the amplifier circuit shown includes a first-stage multi-octave UWB amplifier circuit unit, a second-stage multi-octave UWB amplifier circuit unit and a third-stage multi-octave UWB amplifier unit, image 3 yes figure 2 The block diagram shown corresponds to the circuit schematic. Such as image 3 As shown, the first-stage multi-octave UWB amplifier circuit unit, the second-stage multi-octave UWB amplifier circuit unit and the third-stage multi-octave UWB amplifier un...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More