Rapid-locking low-jitter clock data recovery circuit based on double loops

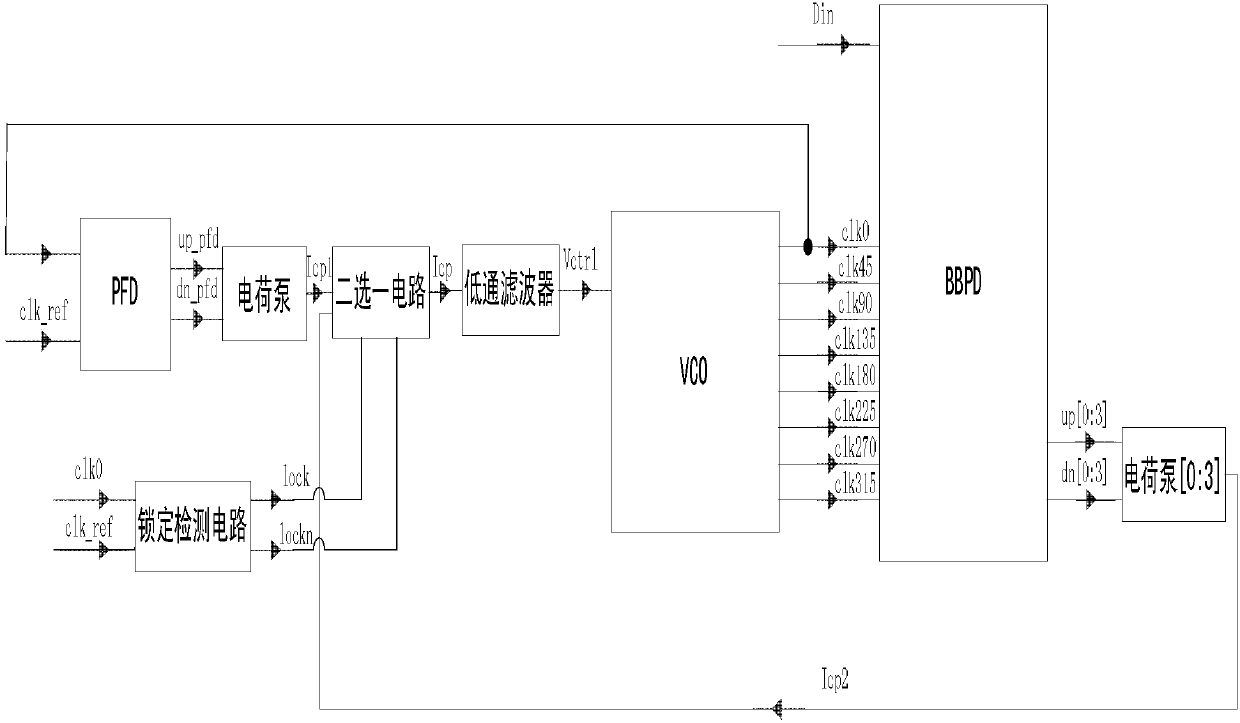

A clock data recovery, low jitter technology, applied in the direction of automatic power control, electrical components, etc., can solve the problem that the clock data recovery circuit cannot have fast locking speed at the same time, and achieve low power consumption, low jitter, and simple structure. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

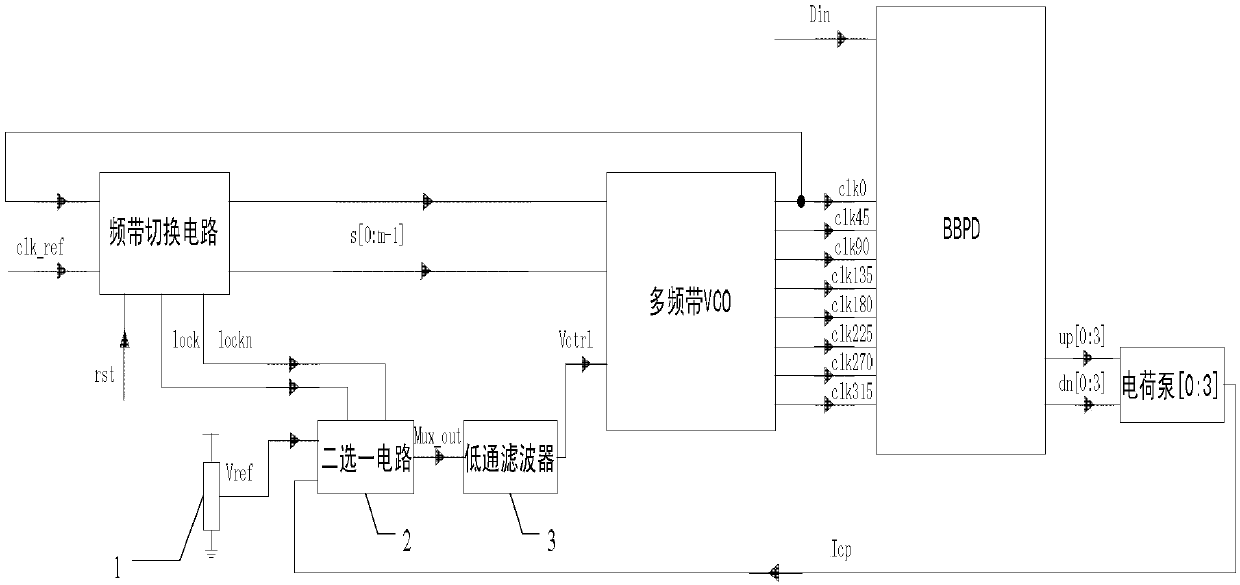

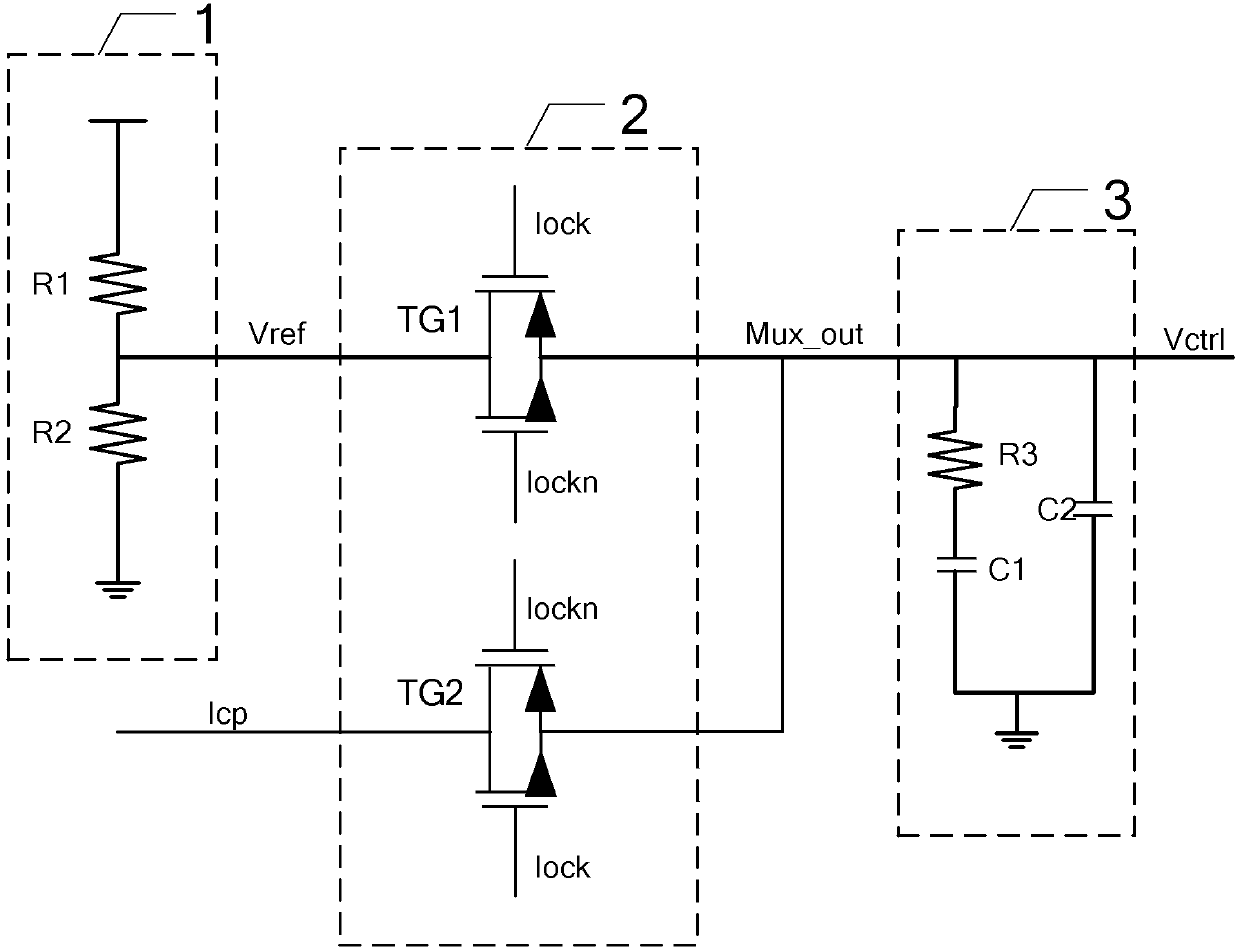

[0027] Specific implementation mode one: combine figure 2 and image 3 Describe this embodiment in detail, the clock data recovery circuit based on double-loop fast locking and low jitter described in this embodiment includes a frequency band switching circuit, a multi-band VCO, BBPD, 4 charge pumps, a low-pass filter, and a resistor divider circuit and alternative circuit;

[0028] The circuit adjusts the frequency band of the multi-band VCO through a frequency-locked loop to achieve frequency locking, and adjusts the control voltage of the multi-band VCO through a phase-locked loop to achieve phase locking;

[0029] Frequency-band switching circuit, multi-band VCO, resistor divider circuit, two-choice circuit and low-pass filter form a frequency-locked loop;

[0030] One-of-two circuit, low-pass filter, multi-band VCO, BBPD, and 4 charge pumps form a phase-locked loop;

[0031] The reference clock input terminal of the frequency band switching circuit is connected to the...

Embodiment

[0047] The clock data recovery circuit is 1 / 4 rate, the input data frequency is 12.5GHz, the reference clock frequency is 3.125GHz, the multi-band VCO has 8 frequency bands in total, and the output 8-phase clock is "011" in the frequency band, and the control voltage is about 3.125GHz clock is output at 580mV, the result of resistor division is 600mV, and the power supply voltage is 1.2V.

[0048] Simulation results such as Figure 4 shown.

[0049] Initial state: The state after reset is the initial state. At this time, the frequency band control word s[0:2] of the multi-band VCO is "000", the lock signal is "0", the lockn signal is "1", and the frequency locking loop is working , the phase-locked loop does not work, and the control voltage of the multi-band VCO is 600mV.

[0050] When the frequency-locked loop is working: the lock signal is "0", the lockn signal is "1", the input terminal of the low-pass filter is connected to the voltage-divider output terminal of the res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More