Measurement method of device surface state traps based on variable frequency pulse technique

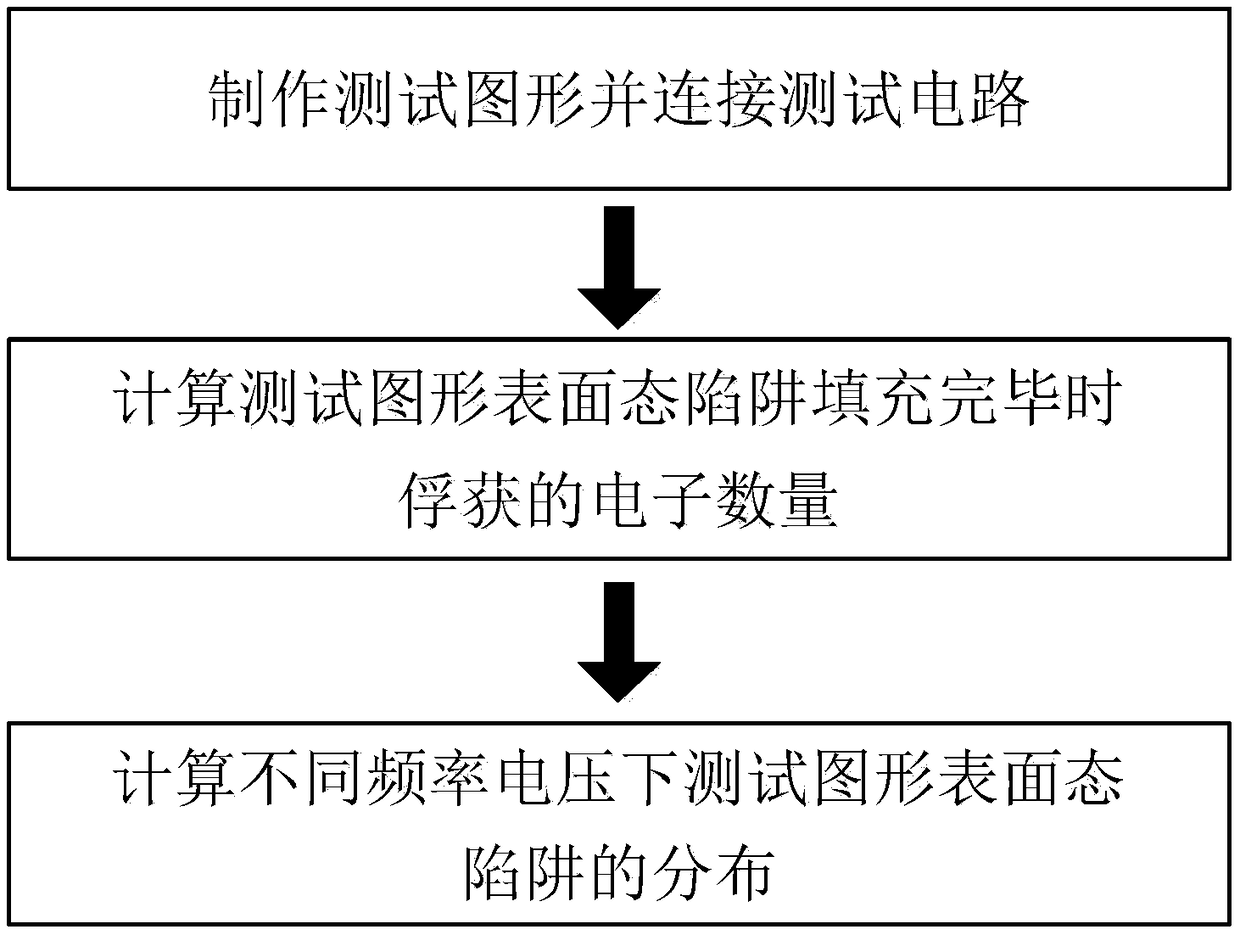

A pulse technology and device surface technology, applied in the field of microelectronic device testing, can solve the problems of reduced device output power, lack of in-depth analysis of surface state physical characteristics, and inability to obtain trap response conditions, achieving simple testing methods and mature process technology. stable effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The specific implementation of the present invention will be further described in detail below in conjunction with the accompanying drawings and examples. The examples are used to illustrate the present invention, but not to limit the scope of the present invention.

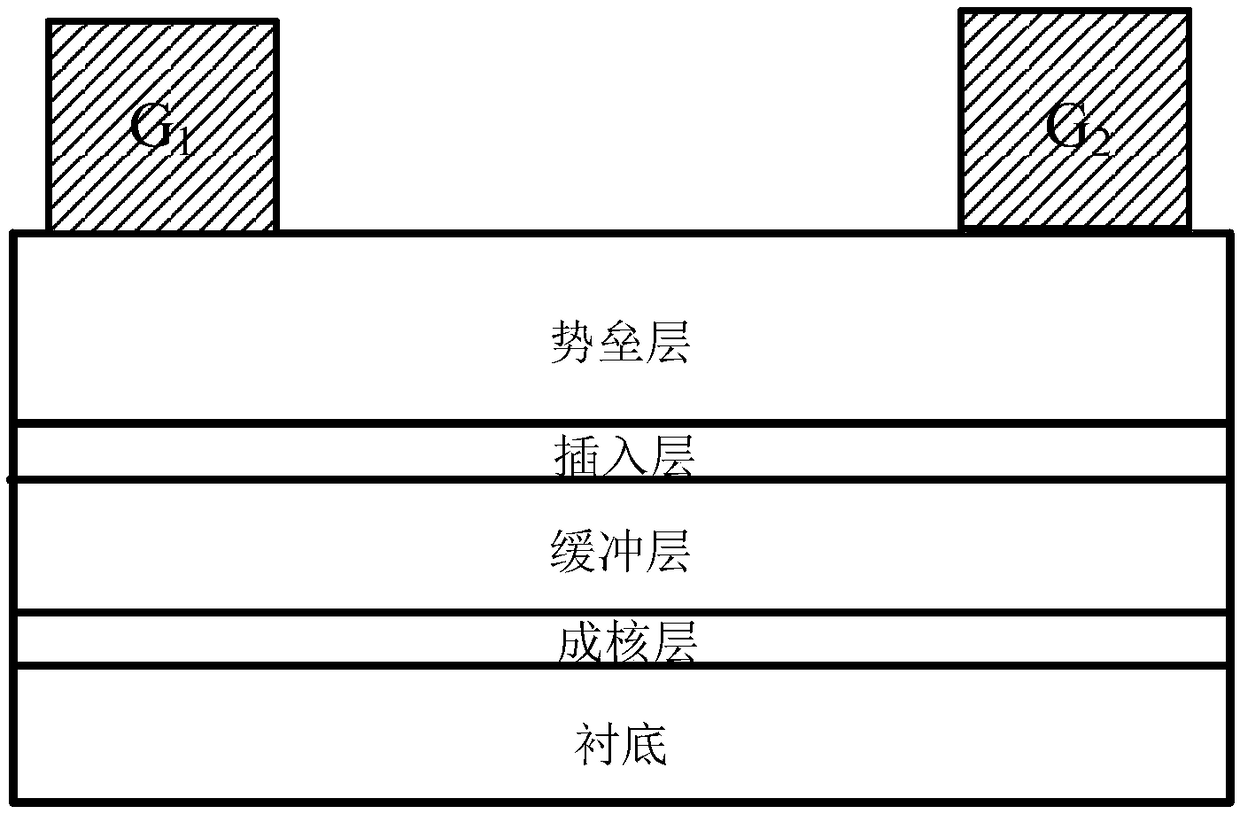

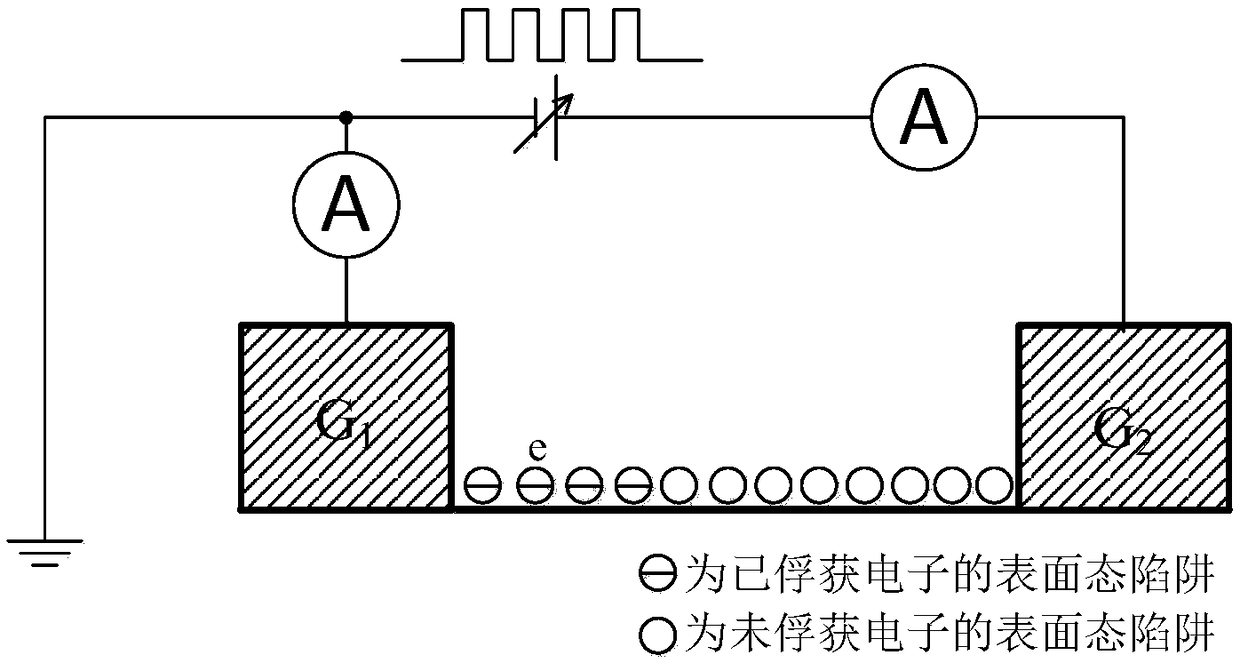

[0037] The devices under test involved in the present invention are three-terminal devices, including but not limited to HEMT devices, MOS devices and JBT devices. The three electrodes of the device under test are gate G, source S and drain D. Since the drain D is an ohmic contact electrode, when the device is working, electrons enter the channel region through the drain D, and then enter the gate G. In this process, electrons will be affected by the traps in the barrier region under the gate G; because the purpose of the present invention is to study the properties of the surface state traps of the device, if the device is directly tested, the traps in the barrier region under the gate G will be introduce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More