Manufacturing method of trench-gate superjunction device

A technology of superjunction device and manufacturing method, which is applied in the manufacture of semiconductor/solid state devices, semiconductor devices, electrical components, etc., can solve the problems of increasing the specific on-resistance of the device, affecting the diffusion of P-type pillars and N-type pillars, etc. The effect of reducing specific on-resistance, reducing leakage, and high doping concentration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0050] Embodiment one method of the present invention:

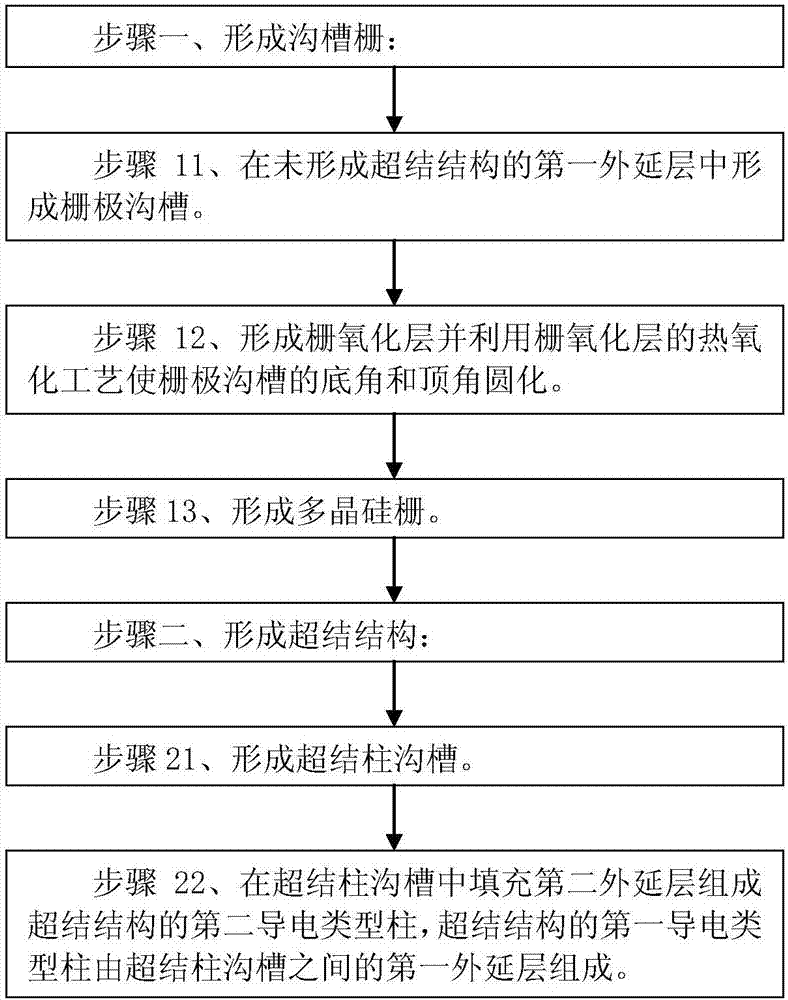

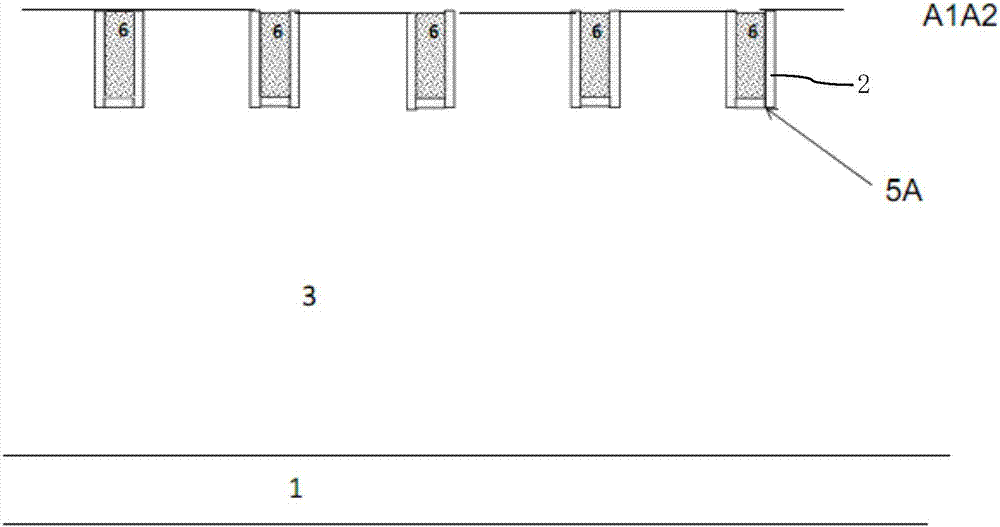

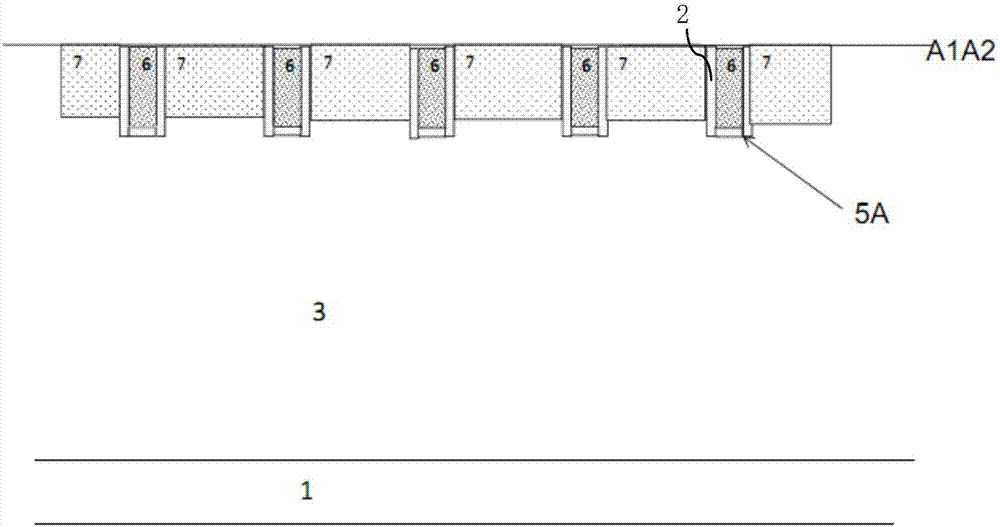

[0051] Such as figure 1 Shown is the flowchart of a method of the embodiment of the present invention; Figure 2 to Figure 7 As shown, it is a schematic diagram of the device structure in each step of the method of the first embodiment of the present invention; the manufacturing method of the trench gate super junction device of the first embodiment of the present invention includes the following steps:

[0052] Step 1, forming the trench gate 6 includes the following sub-steps:

[0053] Step 11, such as figure 2 As shown, the first epitaxial layer 3 of the first conductivity type is provided, and the first epitaxial layer 3 is formed on the surface of the semiconductor substrate 1 of the first conductivity type. The semiconductor substrate 1 in Embodiment 1 of the present invention is a silicon substrate. Bottom, the first epitaxial layer 3 is a silicon epitaxial layer, and the subsequent second epitaxial layer 4 is...

Embodiment 2

[0089] The second method of the embodiment of the present invention:

[0090] The difference between the second method of the present invention and the first method of the embodiment of the present invention is:

[0091] The step of forming the well region 7 of the second conductivity type is performed after step 2, and the step of forming the well region 7 of the second conductivity type is also performed before the deposition process of the field oxide film. The well region of the second conductivity type The implanted area of region 7 is defined using photolithography. In other embodiments, instead of using photolithography to define the injection region of the second conductivity type well region 7 , the second conductivity type well region 7 can be formed by full-scale implantation.

[0092] After the second conductivity type well region 7 is implanted, a high-temperature push-in well is required. In Embodiment 2 of the present invention, the annealing temperature of t...

Embodiment 3

[0094] Embodiment three methods of the present invention:

[0095] The difference between the method of the third embodiment of the present invention and the method of the first embodiment of the present invention is:

[0096] The step of forming the well region 7 of the second conductivity type is performed after step 2, and the step of forming the well region 7 of the second conductivity type is also performed after the patterning process of the field oxide film. The well region of the second conductivity type The implantation of zone 7 was a global implantation.

[0097] Wherein, the step of forming the pattern structure of the field oxide film includes: depositing the field oxide film first, then forming the pattern of the field oxide film by photolithography and etching, and finally forming the pattern in the terminal area, or the terminal area and The field oxide film of 8000 angstroms to 15000 angstroms is formed in the transition area, while the field oxide film is no...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More