Fin field effect transistor and formation method thereof

A fin field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems that the performance of fin field effect transistors needs to be improved, achieve enhanced isolation performance, meet process design, improve The effect of electrical properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] As mentioned in the background, the performance of the FinFETs formed in the prior art needs to be improved.

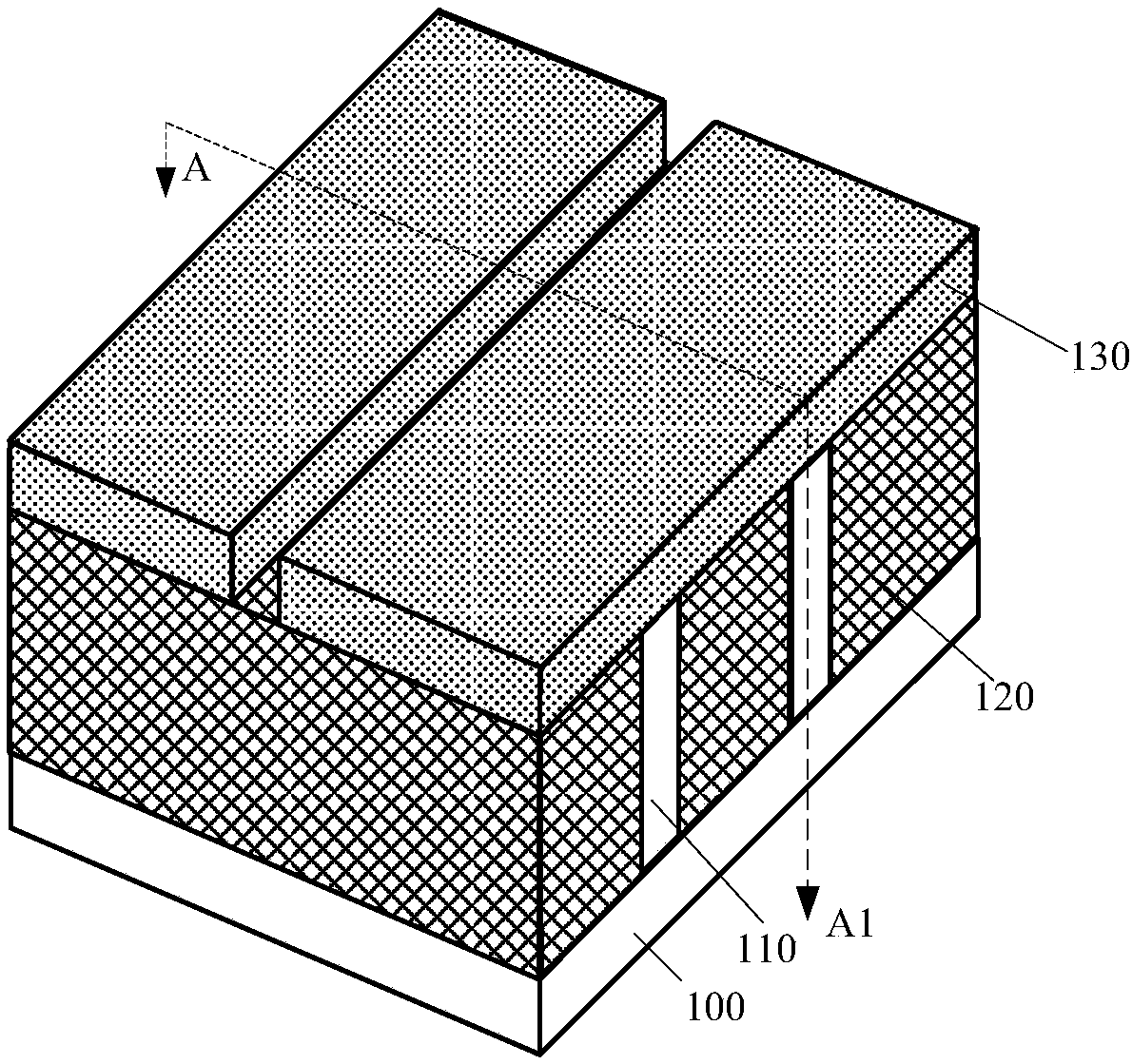

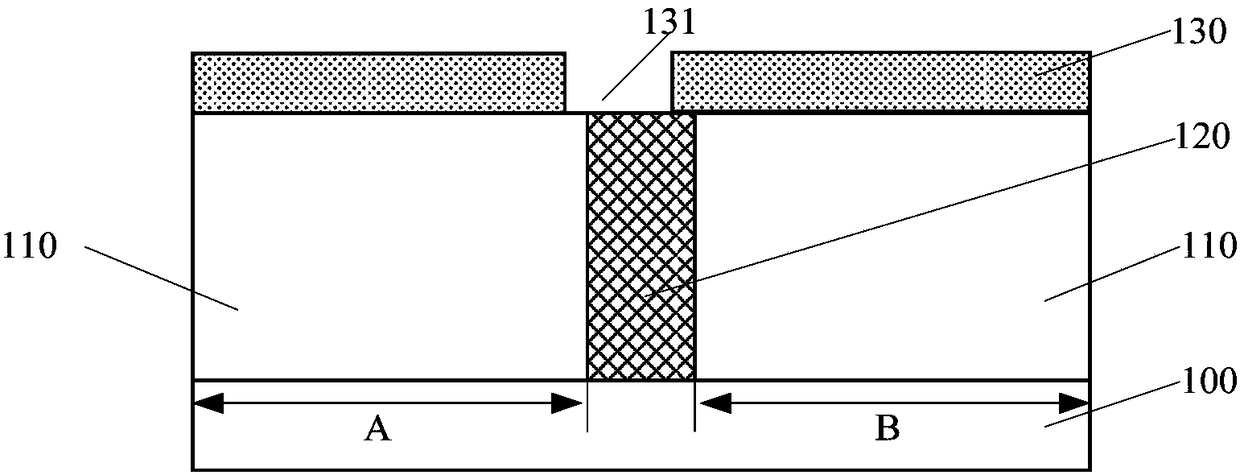

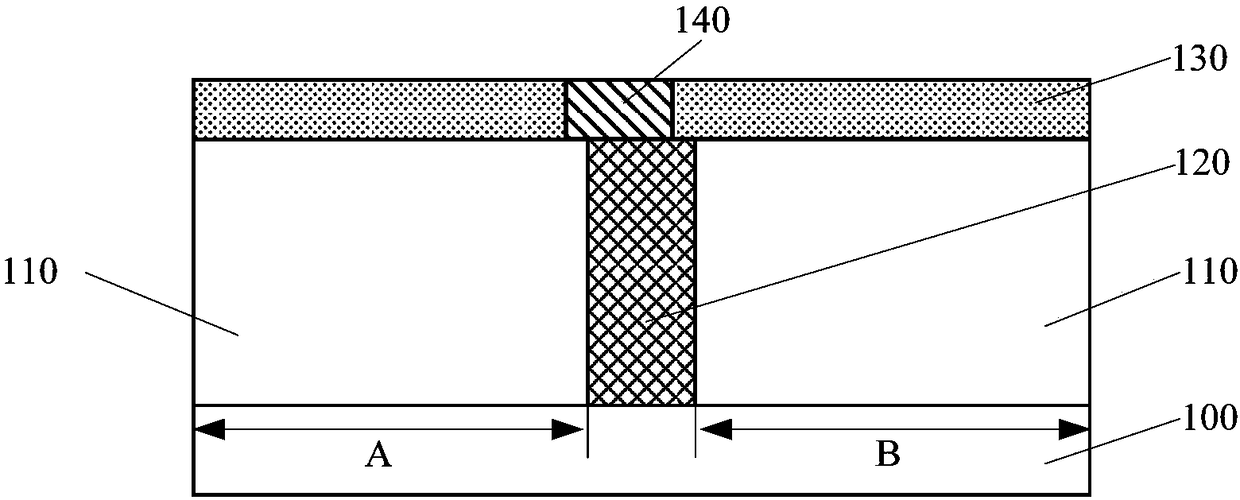

[0036] Figure 1 to Figure 4 It is a structural schematic diagram of the formation process of a fin field effect transistor.

[0037] combined reference figure 1 with figure 2 , figure 2 for along figure 1 A schematic diagram obtained by cutting line A-A1 in the middle, a substrate 100 is provided, and the substrate 100 has a fin portion 110 on it, and the fin portion 110 includes a first region A and a second region B, and between the first region A and the second region B There is an isolation groove (not marked) between them; an isolation structure film 120 covering the sidewall of the fin portion 110 is formed on the substrate 100, and the isolation structure film 120 fills the isolation groove; formed on the isolation structure film 120 and on the fin portion 110 The patterned mask layer 130 has an opening 131 therein, and the opening 131 exposes p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More