Composite material for filling vertical through silicon via (TSV) and filling method thereof

A technology of composite materials and filling methods, which is used in the manufacture of electrical components, circuits, semiconductor/solid-state devices, etc., to achieve the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

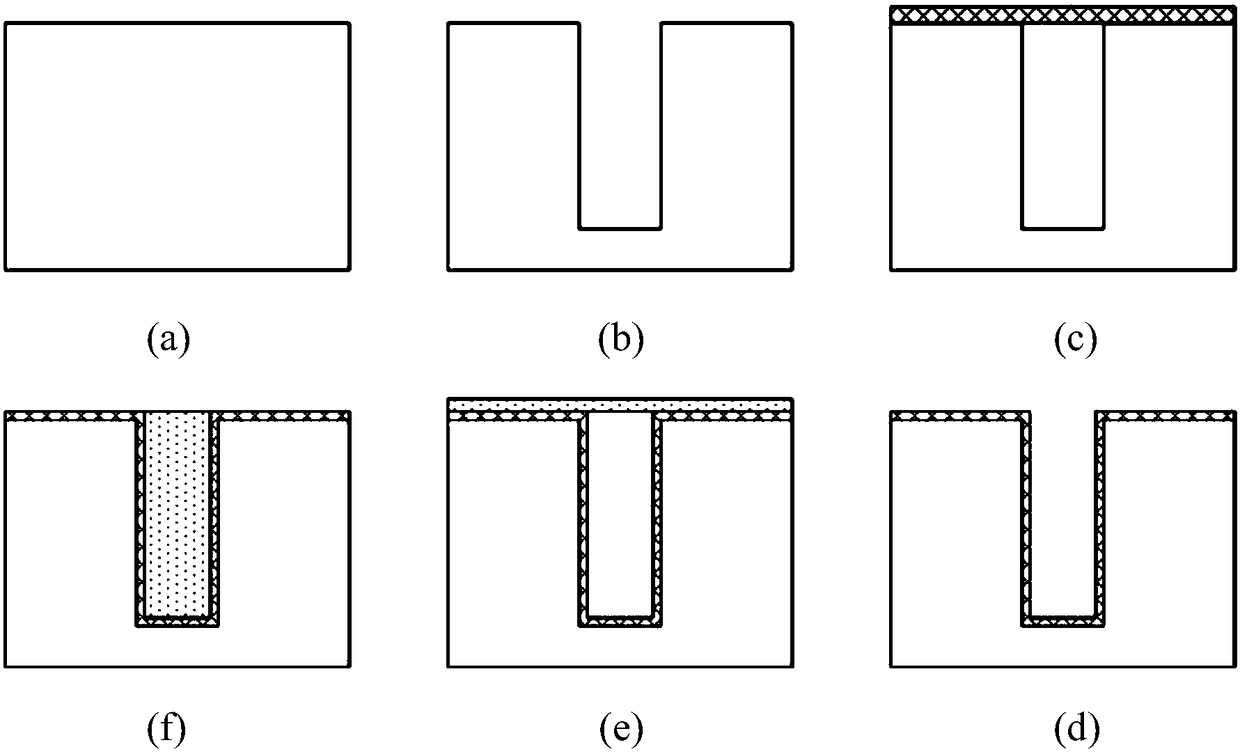

[0052] Step 1: Use deep reactive ion etching (DRIE) or inductively coupled plasma technology (ICP) to etch a through hole on the silicon wafer. The thickness of the silicon wafer is 50um ~ 300um. The hole can be a round hole or a square hole. Pores with a diameter of 0um to 200um and an aspect ratio of 5:1 to 20:1;

[0053] Step 2: Rinse with deionized water to eliminate residual ions on the surface of the wafer and blind holes, and dry in a drying oven under a protective atmosphere;

[0054] Step 3: On the surface of the through hole, an adhesion layer, a barrier layer and a seed layer are sequentially layered. The thickness of the adhesion layer is about 50nm~100nm, the thickness of the barrier layer is about 0.5um~1um, and the thickness of the seed layer is 0.5um~ 1um; the material of the adhesion layer is selected TiN, grown by sputtering method, the material of the barrier layer is selected as SiO2, deposited by vacuum vapor deposition technology, the material of the meta...

Embodiment 2

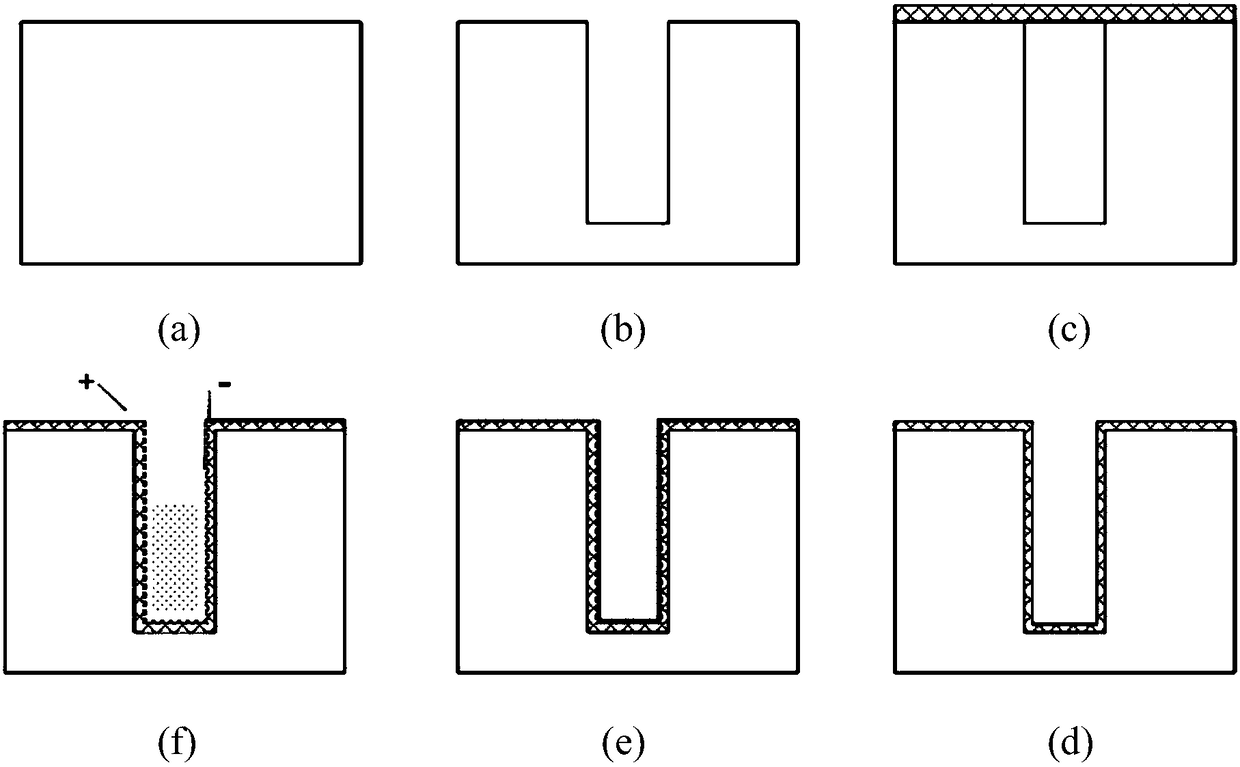

[0076] Step 1: Use deep reactive ion etching (DRIE) or inductively coupled plasma technology (ICP) to etch a through hole on the silicon wafer. The thickness of the silicon wafer is 50um ~ 300um. The hole can be a round hole or a square hole. Pores with a diameter of 0um to 200um and an aspect ratio of 5:1 to 20:1;

[0077] Step 2: Rinse with deionized water to eliminate residual ions on the surface of the wafer and blind holes, and dry in a drying oven under a protective atmosphere;

[0078] Step 3: On the surface of the through hole, an adhesion layer, a barrier layer and a seed layer are sequentially layered. The thickness of the adhesion layer is about 50nm~100nm, the thickness of the barrier layer is about 0.5um~1um, and the thickness of the seed layer is 0.5um~ 1um; the material of the adhesion layer is selected TiN, grown by sputtering method, the material of the barrier layer is selected as SiO2, deposited by vacuum vapor deposition technology, the material of the meta...

Embodiment 3

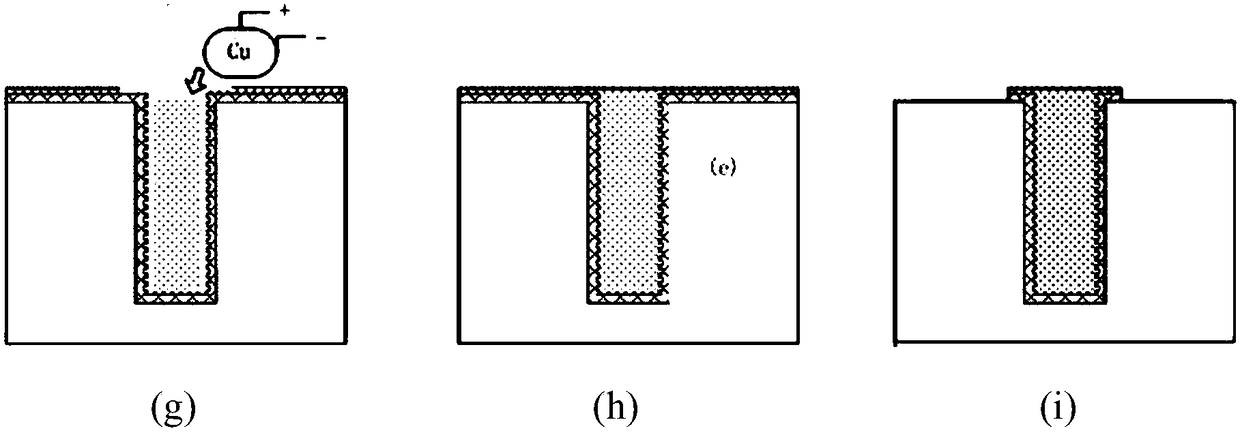

[0100] Step 1: Use deep reactive ion etching (DRIE) or inductively coupled plasma technology (ICP) to etch a through hole on the silicon wafer. The thickness of the silicon wafer is 50um-300um. The pore size is larger than the lower pore size, but not more than 1 / 2. Usually the upper pore size is 50-200um, the lower pore size is 0-150um, and the through-hole aspect ratio is 5:1-20:1;

[0101] Step 2: Rinse with deionized water to eliminate residual ions on the surface of the wafer and blind holes, and dry in a drying oven under a protective atmosphere;

[0102] Step 3: On the surface of the through hole, an adhesion layer, a barrier layer and a seed layer are sequentially layered. The thickness of the adhesion layer is about 50nm~100nm, the thickness of the barrier layer is about 0.5um~1um, and the thickness of the seed layer is 0.5um~ 1um; the material of the adhesion layer is selected TiN, grown by sputtering method, the material of the barrier layer is selected as SiO2, dep...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Thermal expansion coefficient | aaaaa | aaaaa |

| Thermal conductivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More